Final Cut Pro的問題,透過圖書和論文來找解法和答案更準確安心。 我們找到下列懶人包和總整理

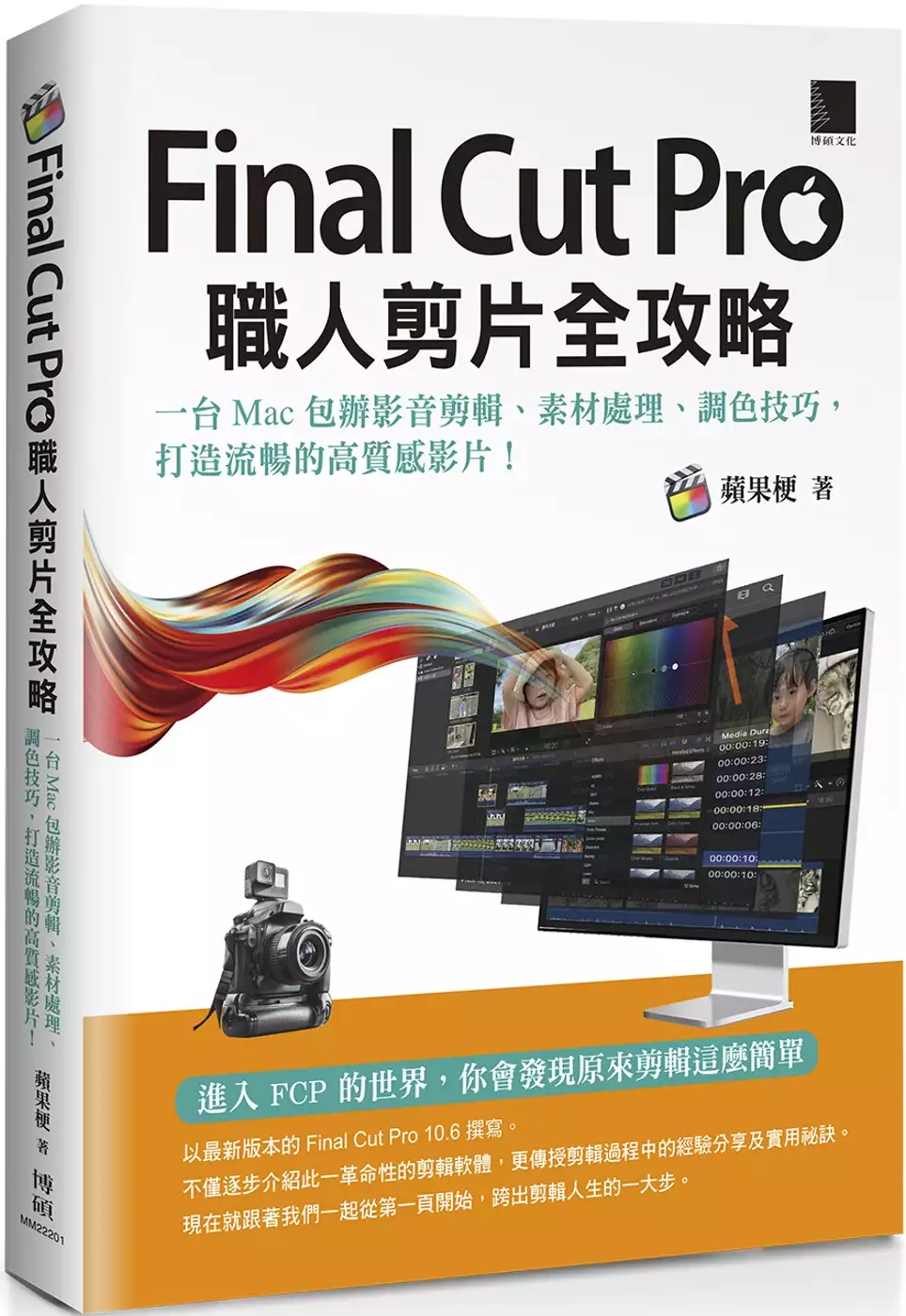

Final Cut Pro的問題,我們搜遍了碩博士論文和台灣出版的書籍,推薦蘋果梗寫的 Final Cut Pro職人剪片全攻略:一台 Mac 包辦影音剪輯、素材處理、調色技巧,打造流暢的高質感影片! 和Nahmani, David的 Logic Pro X - Apple Pro Training Series都 可以從中找到所需的評價。

另外網站Final Cut Pro vs Adobe: Which one is better? - Gitnux Blog也說明:Final Cut Pro is a professional video editing software application developed by Apple Inc. for the Mac platform. It allows users to edit, ...

這兩本書分別來自博碩 和所出版 。

臺北醫學大學 保健營養學系博士班 黃士懿、陳揚卿所指導 NGAN THI KIM NGUYEN的 Precision nutrition for children with early puberty: leveraging nutrigenomics and lipidomics analysis (2021),提出Final Cut Pro關鍵因素是什麼,來自於precocious puberty、central precocious puberty、systematic review、meta-analysis、gene-nutrient interaction、lipidomic analysis、LS/MS、biomarkers。

而第二篇論文長庚大學 奈米工程及設計碩士學位學程 周煌程、杨杰圣所指導 梁文顏的 低功耗高性能電流式感測放大器設計 (2020),提出因為有 電流式電路、感測放大器的重點而找出了 Final Cut Pro的解答。

最後網站How to reclaim disk drive space taken up by Final Cut Pro ...則補充:How to delete the proxies and copies ... Open Final Cut Pro X and select one of your libraries in the upper left corner (Figure A). ... I work with ...

Final Cut Pro職人剪片全攻略:一台 Mac 包辦影音剪輯、素材處理、調色技巧,打造流暢的高質感影片!

為了解決Final Cut Pro 的問題,作者蘋果梗 這樣論述:

拍片很辛苦,剪輯更要有耐心 已經學會iMovie的你,更需要FCP進階技巧,讓每一顆鏡頭都不浪費 進入FCP的世界,你會發現原來剪輯這麼簡單 以最新版本的Final Cut Pro 10.6撰寫。 不僅逐步介紹此一革命性的剪輯軟體,更傳授剪輯過程中的經驗分享及實用祕訣。 現在就跟著我們一起從第一頁開始,跨出剪輯人生的一大步。 Final Cut Pro 一直都是業界最受歡迎的影片剪輯軟體之一。身為專業非線性剪輯軟體的 Final Cut Pro,自從推出 Final Cut Pro X 之後,因為介面與 iMovie 非常類似,吸引了不少使用

者願意開始學習。但是由於多年來沒有繁體中文版本,讓許多人在入門時遇到了不少挫折。 然而儘管剪輯的節奏與美感,是需要天份和更多的經驗累積。但絕對不應該卡在第一步「不知道怎麼使用軟體」。現在就開始打破第一步,拿起本書一起進入 Final Cut Pro 剪輯的有趣世界。 本書作者發揮蘋果教育訓練多年的經驗,從最基礎的介面介紹到實務上的經驗談,一步步的系統化教學,讓每位讀者都能學到許多不為人知的技巧,獨當一面的使用 Final Cut Pro 進行剪輯。 本書特色 ⚙革命性的剪輯方式 ⚙整理素材、剪輯、調色、輸出,一氣呵成 ⚙飛快的專業級效能 ⚙豐富的外掛資源

Final Cut Pro進入發燒排行的影片

訂閱阿宅爸爸的影片 https://tinyurl.com/y9w99rf6

===========================

0歲兒扶著沙發成功站起來了卻...

7年前了,時間過的好快啊!

桐7m13d

5年後..跌倒了不斷站起來學直排輪:

https://youtu.be/gRzHbPnssh4

同場加映,弟弟也扶著同一張無印良品沙發突然就站起來了(咚7m4d):

https://youtu.be/9Vwn_HG4ohk

謝謝您在茫茫人海中點閱我們的影片,

YouTube每天有成千上萬隻影片上傳,實在是難得的緣份,極有可能是一期一會,

歡迎訂閱我們的頻道,常常來看新影片。

如果喜歡我們,覺得影片不錯,也請不要吝嗇幫我們按一個👍讚,

對於我們是莫大的鼓勵,謝謝您

阿宅爸爸的FB跟IG

FB: https://www.facebook.com/otaku.father/

IG: otaku.father https://www.instagram.com/otaku.father

===========================

拍攝工具:

Samsung S10+

GoPro Hero 8

SONY RX100M5A

===========================

剪輯工具:

iMovie

final cut pro

===========================

我的mail:

[email protected]

===========================

幸福有沒有在我身邊,怎麼一直看不見~

爸爸說幸福就在鏡子裡,那就是我快樂的臉~

Precision nutrition for children with early puberty: leveraging nutrigenomics and lipidomics analysis

為了解決Final Cut Pro 的問題,作者NGAN THI KIM NGUYEN 這樣論述:

Background: Precocious puberty (PP) is puberty occurring at an unusually early age that brings in adverse health outcomes during adolescence and adulthood. Pubertal development is a complex biological process of sexual development and is affected by genetic, nutritional, environmental, and socio-ec

onomic factors. However, the relationship between pre-pubertal intakes of energy, fat, fiber, protein levels and pubertal timing has been debated. In the genomic era, it is necessary to examine the individual response to a specific diet and how diet influences metabolic regulation in children with P

P personally. Limited evidence investigated the timing of pubertal onset by examining the interaction of nutrient intake and PP-related genetic loci. Importantly, endocrine disorders can alter lipid metabolism. The fact that puberty onset requires critical weight and body fat based on the “critical

weight hypothesis” and many lipid species have been noticed in many human obesity and metabolic syndrome studies. However, a lack of evidence works on lipidomes to propose the based-lipid biomarker and lipid metabolism in predicting PP in children.Methods: By performing a systematic review and meta-

analysis of prospective studies, we aimed to disclose the role of pre-pubertal and pubertal nutrient intake in PP development. Thereafter, we conducted a Taiwan Puberty Longitudinal Study (TPLS) in recruiting adolescents from pubertal and pediatric endocrine clinics in the Northern/Southern part of

Taiwan. The buccal samples for deoxyribonucleic acid (DNA) extraction and genotyping were collected from a total of 1404 children. We will examine the nutrient intake on the interaction with PP-related SNPs on pubertal timing using the “interaction term” of logistic regression. Also, lipidomic analy

sis deriving from 178 subjects’ plasma samples was used to identify the critical lipid biomarkers in diagnosing PP and central precocious puberty (CPP).Results: A high intake of protein, particularly animal protein, monounsaturated fatty acids (MUFAs), polyunsaturated fatty acids (PUFAs) among prepu

bertal girls were significantly associated with PP risk. We also found that SNP rs12617311, rs2090409, and rs12148769 were significantly associated with PP in children. Specifically, different genotypes interacted with such food groups and micronutrient intake. A significant interaction was observed

between intake of vegetables, fruits, fructose and menarcheal loci rs12617311 (PCL1). The rs2090409 (TMEM38B) was more likely to interact with vitamin intake. Importantly, rs12148769 (MKRN3) appeared a significant interaction with saturated FA and MUFA intake. Whist, SNP rs10980921 (ZNF483) showed

a significant interaction with total PUFAs intake. The intake of sucrose, MUFAs, and PUFAs was associated with the potential lipid-based biomarkers, such as Cer(d16:1/22:0), PI(18:2/22:1), and PI(18:2/22:2) of girls and Cer(t20:0/18:0), Cer(d18:1/16:0) and Cer(d18:1/18:1) of boys that could predict

PP and CPP onset. In addition, the lipidomic analysis proposed several candidate lipids metabolism pathways, such as sphingolipid metabolism, steroid biosynthesis, and bile acid biosynthesis for an in-depth lipid mechanism that can be linked to PP and CPP pathophysiology.Conclusion: There was an int

eraction between genetic variant, lipid metabolism, and nutrient intake that was convinced to be associated with PP and CPP development in girls and boys. Nutrient intake may be an important factor in modulating early puberty, especially the consumption of sugar, fructose, and specific saturated fat

ty acids, monounsaturated fatty acids, polyunsaturated fatty acids. Additional research is needed to determine the biological causes of individual variability in response to dietary intake. Likewise, understanding the influence of nutrigenetic interactions on dyslipidemia can aid in the development

and implementation of personalized dietary strategies to improve the PP and CPP treatment.

Logic Pro X - Apple Pro Training Series

為了解決Final Cut Pro 的問題,作者Nahmani, David 這樣論述:

The Apple-Certified Way to Learn Record, arrange, produce, mix, and master music with this bestselling, Apple-certified guide to Logic Pro. Veteran producer and composer David Nahmani uses real-world professional Logic Pro projects to guide you through step-by-step instructions and straightforwar

d explanations, ranging from basic music creation to sophisticated production techniques.You’ll trigger Live Loops in real time, record audio and software instruments, create and edit sequences, and build arrangements. You’ll create both acoustic and electronic virtual drum performances. You’ll use

Quick Sampler to create stutter effects and vocal chop, and explore ear candy production techniques, such as parallel processing and turntable start and stop effects. You’ll use Smart Controls to map knobs, buttons, and drum pads on a MIDI controller or an iPad. You’ll harness the power of Smart Tem

po to sync up all your audio and MIDI. You’ll use Flex Time to stretch audio and correct the timing of recordings, and you’ll tune vocals with Flex Pitch. You’ll mix, automate, and master the song with EQ, compression, delay, reverb, limiters, and other plug-ins to achieve a professional sound. Fina

lly, you’ll create a 3D spatial audio mix with Logic Pro’s new Dolby Atmos plug-ins, using binaural rendering to experience that immersive sonic experience on your headphones.Downloadable real-world, professional Logic projectsStep-by-step hands-on exercisesAccessible writing style that puts an expe

rt mentor at your sideAmple illustrations that help you quickly master techniquesLists of keyboard shortcuts used in each lessonTips to improve your workflowOnline personal support on the author’s websiteThe Apple Pro Training Series is Apple’s official self-paced learning resource. Books in this se

ries offer downloadable lesson files and an online version of the book. Additional information on this and other books in this series can be found at peachpit.com/apple. For more on certification, visit training.apple.com.Also in the Apple Pro Training Series: Final Cut PromacOS Support Essentials

低功耗高性能電流式感測放大器設計

為了解決Final Cut Pro 的問題,作者梁文顏 這樣論述:

Table of ContentsRecommendation Letters from Thesis AdvisorsThesis/Dissertation Oral Defense Committee CertificationPreface iiiAbstract ivTable of Contents vList of Figures viiList of Tables xiChapter 1 Introduction 11.1 Memory and Processors 21.2 Sense Amplifiers 31.3 Technology Trends 41.4 Circui

t Trends 51.5 Other Trends 61.6 SRAM Trends 71.7 Associated Challenges 9Chapter 2 A Circuits Survey 102.1 The Two Broad Classes 102.2 Voltage Sensing 122.3 Current Sensing 162.4 Others 20Chapter 3 Development of a Three-Transistor I–V Converter 223.1 Low Drop-Out Voltage Regulator as a I–V Converter

233.2 I–V Converter as a Current Sense Amplifier 253.3 Simplifying the I–V Converter 253.4 Proof of Concept 273.5 Quest for a Better Error Amplifier 293.6 Revisiting the Proof of Concept 31Chapter 4 Implementation of a Current Sense Amplifier 344.1 Sense Amplifier Shut-Down 344.2 Static Power Reduc

tion 364.3 Pulsed Word-Line Operation 374.4 Bit-Line Capacitance—Effect on Delay 394.5 Bias Variation 414.6 Relevant Concerns 43Chapter 5 Conclusion 445.1 Simulation Results 445.2 Considerations for Long Bit-Lines 465.3 Measurements 475.4 Derivative Circuits 495.5 Derivative Use 525.6 Summary 555.7

Final Thoughts 55References 56Appendices 83List of FiguresFigure 1.1 Die micrograph from [Singh et al., 2018] 2Figure 1.2 Layout from [Takemoto et al., 2020] 2Figure 1.3 Package from [Poulton et al., 2019] 4Figure 1.4 Wearable for happiness index from [Yano et al., 2015] 6Figure 1.5 Test chip from [

Song et al., 2017] 7Figure 2.1 Left–right: nMOS common-source, -gate and -drain amplifier configurations 10Figure 2.2 Left–right: pMOS common-drain, -gate and -source amplifier configurations 11Figure 2.3 Bi-stable constructed of two inverters 11Figure 2.4 Regenerative latch transient simulation out

put 11Figure 2.5 nMOS differential pair 12Figure 2.6 nMOS–input pair differential amplifier 13Figure 2.7 Clocked latch with isolation 14Figure 2.8 Current-controlled latch 15Figure 2.9 Left–right: Resistor and nMOS approximates 16Figure 2.10 Left–right: Resistor and pMOS approximates 16Figure 2.11 n

-p-n common-base amplifier 17Figure 2.12 Partial schematic from [Yeo and Rofail, 1995] 17Figure 2.13 Left–right: nMOS and pMOS current mirrors 18Figure 2.14 Current sense amplifier from [Ishibashi et al., 1995] 18Figure 2.15 Current sense amplifier from [Seno et al., 1993] 19Figure 2.16 Current conv

eyor from [Seevinck et al., 1991] 19Figure 2.17 pMOS-neutralised nMOS differential pair 20Figure 2.18 Λ-type negative resistance from [Wu and Lai, 1979] 21Figure 2.19 I D -V D characteristic of the Λ-type negative resistance 21Figure 3.1 Three-transistor I–V converter 22Figure 3.2 Simplified low dro

p-out voltage regulator 23Figure 3.3 Low drop-out voltage regulator configured as a I–V converter 24Figure 3.4 Low drop-out voltage regulator as a current sense amplifier 25Figure 3.5 Reference-free I–V converter 26Figure 3.6 Logic inverters as positive-gain amplifier 26Figure 3.7 Proof of concept d

esign 27Figure 3.8 Proof of concept design transient simulation output 28Figure 3.9 Typical and unintended input(s) of the logic inverter 29Figure 3.10 Normalised absolute gain plot for each inverter input 30Figure 3.11 Connections made for the absolute gain plot 30Figure 3.12 Bias generator for the

absolute gain plot 31Figure 3.13 Error amplifier replacement in the proof of concept design 31Figure 3.14 Three-transistor I–V converter 32Figure 3.15 Corresponding bias generator of Figure 3.14 32Figure 3.16 Simulation circuit for verifying the improved error amplifier 33Figure 3.17 Demonstration

of the three-transistor I–V converter as a current sense amplifier 33Figure 4.1 Actions to achieve desired node characteristics during shut-down 34Figure 4.2 Figure 3.14 modified for shut-down 35Figure 4.3 Corresponding bias generator of Figure 4.2 35Figure 4.4 Shared use of bias generator 36Figure

4.5 Pseudo-differential version of Figure 4.4 37Figure 4.6 Pseudo-differential configuration of Figure 3.14 37Figure 4.7 Pulsed read of a ZERO 38Figure 4.8 Pulsed read of a ONE 38Figure 4.9 Differential development across dynamic bit-lines and csa outputs 39Figure 4.10 Delay behaviour with capacitiv

e bit-line loading 40Figure 4.11 Normalised csa bias current variation with supply voltage 41Figure 4.12 Normalised csa bias current variation with temperature 42Figure 4.13 Mismatch view of Figure 3.14 43Figure 5.1 Test set-up (external trigger connection not drawn) 47Figure 5.2 Oscillogram demonst

rating circuit functionality at VDD = 2.55V 47Figure 5.3 Test set-up photograph 48Figure 5.4 Left–right: Three-transistor I–V converter and its complement 49Figure 5.5 Transfer characteristics of the circuits in Figure 5.4 49Figure 5.6 Four-transistor I–V converter 50Figure 5.7 Corresponding bias ge

nerator of Figure 5.6 50Figure 5.8 Impact of sizing on AC performance 51Figure 5.9 Left–right: V SS -, V DD -referenced and floating optical receiver front ends 52Figure 5.10 Transfer characteristic of floating I–V converter 53Figure 5.11 High output resistance eases filter realisation 53Figure 5.12

Three-transistor I–V converter operating as an open-drain receiver 54Figure A.1 inv symbol 84Figure A.2 Alternate inv symbol 84Figure A.3 inv transistor-level schematic 84Figure A.4 inv4 symbol 85Figure A.5 inv4 transistor-level schematic 85Figure A.6 inv16 symbol 86Figure A.7 inv16 transistor-leve

l schematic 86Figure A.8 nand2 symbol 87Figure A.9 nand2 transistor-level schematic 87Figure A.10 nand2b symbol 88Figure A.11 nand2b gate-level schematic 88Figure A.12 nor2 symbol 89Figure A.13 nor2 transistor-level schematic 89Figure A.14 nor2b symbol 90Figure A.15 nor2b gate-level schematic 90Figu

re A.16 or2 symbol 91Figure A.17 or2 gate-level schematic 91Figure A.18 tinv symbol 92Figure A.19 tinv transistor-level schematic 92Figure A.20 dlat symbol 93Figure A.21 dlat gate-level schematic 93Figure A.22 dlatr symbol 94Figure A.23 dlatr gate-level schematic 94Figure A.24 dlats symbol 95Figure

A.25 dlats gate-level schematic 95Figure A.26 tie0 symbol 96Figure A.27 tie0 transistor-level schematic 96Figure A.28 tie1 symbol 97Figure A.29 tie1 transistor-level schematic 97Figure B.1 bit0 symbol 99Figure B.2 bit0 transistor-level schematic 99Figure B.3 bit1 symbol 100Figure B.4 bit1 transistor

-level schematic 100Figure B.5 blrc symbol 101Figure B.6 blrc cell-level schematic 101Figure B.7 pre symbol 102Figure B.8 pre transistor-level schematic 102Figure B.9 rblrc symbol 103Figure B.10 rblrc cell-level schematic 103Figure B.11 wr symbol 104Figure B.12 wr transistor-level schematic 105Figur

e B.13 anand2 symbol 106Figure B.14 Alternate anand2 symbol 106Figure B.15 anand2 transistor-level schematic 107Figure B.16 ckgen symbol 108Figure B.17 ckgen gate-level schematic 108Figure B.18 peri symbol 109Figure B.19 peri cell-level schematic 110Figure B.20 csa symbol 111Figure B.21 csa transist

or-level schematic 111Figure B.22 kobl symbol 112Figure B.23 Alternate kobl symbol 112Figure B.24 kobl transistor-level schematic 113Figure B.25 kobs symbol 114Figure B.26 kobs transistor-level schematic 114Figure C.1 sram1 symbol 116Figure C.2 sram1 block-level schematic 117Figure C.3 sram2 symbol

118Figure C.4 sram2 block-level schematic 119Figure C.5 sram3 symbol 120Figure C.6 sram3 block-level schematic 121Figure D.1 ainvl symbol 123Figure D.2 ainvl transistor-level schematic 123Figure D.3 ainvs symbol 124Figure D.4 Alternate ainvs symbol 124Figure D.5 ainvs transistor-level schematic 124F

igure D.6 cut symbol 125Figure D.7 cut cell-level schematic 126Figure D.8 inAmp symbol 127Figure D.9 inAmp cell-level schematic 127Figure D.10 CD4007 symbol 128Figure D.11 CD4007 transistor-level schematic 128Figure D.12 LF356 symbol 129Figure D.13 LF356 cell-level schematic 129Figure D.14 TL431 sym

bol 130Figure D.15 TL431 cell-level schematic 130Figure D.16 tialp symbol 131Figure D.17 tialp transistor-level schematic 131Figure D.18 tiasd symbol 132Figure D.19 tiasd transistor-level schematic 132Figure D.20 tiasn symbol 133Figure D.21 tiasn transistor-level schematic 133Figure D.22 tiasp symbo

l 134Figure D.23 tiasp transistor-level schematic 134Figure E.1 nfet and equivalent nMOS symbol 135Figure E.2 pfet and equivalent pMOS symbol 136Figure E.3 Circuit for estimating per-bit junction capacitance 137Figure E.4 Simulation output for estimating per-bit junction capacitance 138Figure E.5 Ci

rcuit for estimating per-bit bit-line leakage current 138Figure E.6 ID-VD characteristics 139Figure E.7 ID-VG characteristics 140Figure E.8 anand2 transistor-level schematic 141Figure E.9 Test board functional blocks 144Figure E.10 Test board block-level schematic 145Figure E.11 Signal source connec

ted to abbreviated input network 148Figure E.12 General form of a typical instrumentation amplifier 150Figure E.13 Inverting integrator section of test board 154List of TablesTable 1.1 Semiconductor memory hierarchy 1Table 5.1 Column height h = 512b 44Table 5.2 Column height h = 1Kb 44Table 5.3 Colu

mn height h = 2Kb 44Table 5.4 Summarised measurement results 48Table A.1 List of standard cells 83Table A.2 inv truth table 84Table A.3 inv4 truth table 85Table A.4 inv16 truth table 86Table A.5 nand2 truth table 87Table A.6 nand2b truth table 88Table A.7 nor2 truth table 89Table A.8 nor2b truth tab

le 90Table A.9 or2 truth table 91Table A.10 tinv truth table 92Table A.11 dlat truth table 93Table A.12 dlatr truth table 94Table A.13 dlats truth table 95Table A.14 tie0 truth table 96Table A.15 tie1 truth table 97Table B.1 List of custom cells 98Table B.2 pre truth table 102Table B.3 wr truth tabl

e 104Table C.1 SRAM cells and read path configurations 115Table D.1 List of other cells 122Table E.1 Transistor performance 140Table E.2 Primary bill of materials 146Table E.3 Additional hardware 147Table E.4 List of instruments 155Table F.1 List of abbreviations 158Table F.2 List of symbols 159Tabl

e F.3 List of AC quantities 160Table F.4 List of DC quantities 161Table F.5 List of partial-swing signals 162Table F.6 List of rail–rail signals 162Table F.7 List of instance names 163

想知道Final Cut Pro更多一定要看下面主題

Final Cut Pro的網路口碑排行榜

-

#1.[Final Cut Pro教學]專業影片剪輯軟體特色介紹、費用和優缺點!

Final Cut Pro 是一款專業的視頻剪輯軟體,可支援MacOS作業系統,如果你本身就是Mac 的用戶那麼這套軟體將是你的不二之選。 近年來Apple 的產品逐漸邁向 ... 於 soonotes.com -

#2.21 power tips & tricks to become a Final Cut Pro X professional

9. Final Cut Pro X Shortcuts · E : you can 'append edit' a clip from the Browser into the Timeline simply by tapping the E key · Shift+Z : if you need to fit ... 於 www.instrumentalbackgroundmusic.com -

#3.Final Cut Pro vs Adobe: Which one is better? - Gitnux Blog

Final Cut Pro is a professional video editing software application developed by Apple Inc. for the Mac platform. It allows users to edit, ... 於 blog.gitnux.com -

#4.How to reclaim disk drive space taken up by Final Cut Pro ...

How to delete the proxies and copies ... Open Final Cut Pro X and select one of your libraries in the upper left corner (Figure A). ... I work with ... 於 www.techrepublic.com -

#5.Final Cut Pro X vs Adobe Premiere Pro The Ultimate Video ...

However, when you become a professional video editor, there is one choice you need to make. It's between Adobe Premiere Pro or Final Cut Pro X. Adobe ... 於 earing.wiki -

#6.Final Cut Pro Templates - Envato Elements

Download hundreds of high-quality and easy-to-use assets for Final Cut Pro. Helping with intros, titles, lower thirds, logos or transitions. 於 elements.envato.com -

#7.Editing Techniques with Final Cut Pro - 第 335 頁 - Google 圖書結果

Final Cut Pro provides tools aimed specifically at solving these problems. Use the Vocal DeEsser filter to remove excessive sibilance. 於 books.google.com.tw -

#8.FCPX插件-50个现代创意抽象文字排版海报动态视觉预设

系统要求:Mac 苹果电脑系统(Win系统不支持) 芯片兼容:支持Intel和Apple M芯片软件要求:Final Cut Pro X 10.6 和更高版本文件大小:85M(.dmg ... 於 www.lookae.com -

#9.Mastering Final Cut Pro - Coursera

Students will dive into the key features of Apple's Final Cut Pro software for Video and Audio Editing and learn elements for creating professional videos ... 於 tw.coursera.org -

#10.Final Cut Pro | Updates, Features, Prices - AppleInsider

Final Cut Pro is Apple's professional-level, non-linear, non-destructive video editing software. Originally designed by Macromedia in the mid-90s, ... 於 appleinsider.com -

#11.Final Cut Pro X vs. Premiere Pro - Adobe

Understand why video editors and pro social creators are switching from Final Cut Pro X to Adobe Premiere Pro. Automate tasks and control workflow with ... 於 www.adobe.com -

#12.Final Cut Pro - Apple Wiki | Fandom

Final Cut Pro was a professional non-linear video editing system developed by Apple. It was targeted towards high-end video hobbyists and independent ... 於 apple.fandom.com -

#13.用於Final Cut Pro X 的Canon RAW Plugin 2.2

用於Final Cut Pro X 的Canon RAW Plugin 2.2 是一款在Apple Inc. 生產的macOS 系統上運行的外掛程式軟件,可透過Final Cut Pro 匯入和編輯Canon ... 於 tw.canon -

#14.MarkUp for Final Cut Pro - FxFactory

Annotate your screen captures and video presentation materials with MarkUp. Exclusively made for Final Cut Pro, add animated tools that draw attention and ... 於 fxfactory.com -

#15.Final Cut Pro Learning Path - Ripple Training

Final Cut Pro Tutorials That Make Every Second Count. With your busy schedule, the last thing you want is to sit through hours of unfocused ... 於 www.rippletraining.com -

#16.為什麼你需要花$9900 買FINAL CUT PRO? - YouTube

前兩集我們提到了5 個iMovie 上的功能來和 Final Cut Pro 做對比,那今天我們來聊聊另外五個功能來做比較,讓你了解什麼時候該考慮從iMovie 升級 ... 於 www.youtube.com -

#17.零基礎剪輯新手10 分鐘學會Final Cut Pro X // 必知功能(2022 ...

免費下載5 組我們的Lightroom 調色檔: https://bit.ly/3HydiwD 藍諾攝影學院: https://bit.ly/3KKEHhn18 堂課學會 Final Cut Pro X: ... 於 www.youtube.com -

#18.final cut pro白平衡 - 抖音

抖音为你提供final cut pro白平衡短视频信息,帮你找到更多精彩的白平衡视频内容!让每一个人看见并连接更大的世界,让现实生活更美好. 於 www.douyin.com -

#19.The Best Final Cut Pro Templates | Motion Array

Final Cut Pro is a video editing software by Apple Inc. Like most editing software these days, it enables non-linear editing (NLE). In other words, it lets ... 於 motionarray.com -

#20.ryan fcpx transitions - Croce Verde Pignone

3 + Pro Exporter Pack for Final Cut Pro X and Motion 5 (Mac O fcpx转场插件12组镜头透视旋转效果过渡转场这是一套包含了12组模拟镜头透视旋转效果的过渡转场,在旅 ... 於 croceverdepignone.it -

#21.Final Cut Pro X 10.1.2 專業剪輯主題課程 - Facebook

主題課程(收費) 7/28(一) 晚上19:00~22:00 FCP X 拍攝母帶與剪輯資料庫管理 3小時... ... Final Cut Pro X 10.1.2 專業剪輯主題課程. 於 www.facebook.com -

#22.free fcpx - GMG Dipinture

With some of the best Final Cut Pro effects, the software provides an ... Free DataPop Oct 10, 2022 · 50+ Best Free Final Cut Pro (FCP) Templates, Plugins, ... 於 gmgdipinturemonetti.it -

#23.mMotion Blur — Adjustable Motion Blur for Final Cut Pro

With the mMotion Blur plugin for Final Cut Pro, you can easily add this effect to your entire timeline. Simply fine-tune the parameters to boost the ... 於 www.motionvfx.com -

#24.How to add text and titles in Final Cut Pro X - Filmstro

The simplest way to add titles or text to your video clip is to go straight to Edit > Connect Title > Basic Title. This will then pop up a text- ... 於 filmstro.com -

#25.盜版Mac剪輯軟體Final Cut Pro內含惡意挖礦程式 - iThome

而Jamf發現盜版的Final Cut Pro經過非Apple官方的修改,會在後臺執行XMRig。該惡意挖礦軟體使用i2p(Invisible Internet Project)進行通訊,而i2p是一個 ... 於 www.ithome.com.tw -

#26.Final Cut Pro X 10 4 6 Review Apple Refines Stalwart Video ...

2 Final Cut Pro X 10. 6 Lifewire / Todd Braylor Pleasants What We Like Supports 4K, 8K and VR video editing Advanced post-production color ... 於 commitment.wiki -

#27.Final Cut Pro - Frame.io

Frame.io lets you share cuts, view stakeholder feedback, and manage the entire project — all without ever leaving Final Cut Pro. This is next-level speed and ... 於 frame.io -

#28.Final Cut Pro - Apple (台灣)

Final Cut Pro 能為在iPhone 13 上拍攝的「電影級」模式影片,帶來全然一新的面貌。透過創新突破的點按追蹤功能,你可以選擇畫面中的焦點,並隨著時間推進而變化焦點。你也 ... 於 www.apple.com -

#29.Final Cut Pro X影音剪輯國際認證班 - 中國文化大學推廣教育部

Final Cut Pro X是蘋果公司所推出的一套專業的非線性媒體編輯軟體,其提供強大而精確的編輯工具,幾乎能夠處理任何格式,是目前電影工業用來剪接影片最佳的軟體! 於 www.sce.pccu.edu.tw -

#30.Final Cut Pro X Plugins | Effects, Transitions, Themes, Tools ...

Plugins for Final Cut Pro X. 1000's of effects, transitions, themes and text presets for Final Cut Pro X. Design video graphics for Final Cut using Pixel ... 於 store.pixelfilmstudios.com -

#31.Pirating Final Cut Pro Is More Dangerous Than You Think

However, the malware Jamf Threat Labs discovered in pirated copies of Final Cut Pro isn't necessarily designed to steal your information or ... 於 lifehacker.com -

#32.Premiere Pro vs. Final Cut Pro: Which one is better?

Final Cut Pro is a heavy-duty option with fast render speeds and a streamlined UI for chronological video projects. It offers a one-time payment ... 於 www.videomaker.com -

#33.DaVinci Resolve vs Final Cut Pro Which One Is the Better Non ...

It may come down to these choices if you're on a Mac-Premiere Pro, DaVinci Resolve, and Final Cut Pro. Both DaVinci Resolve and Final Cut Pro outperform ... 於 have.wiki -

#34.Download Free Final Cut Pro Templates - Mixkit

Download from our library of free Final Cut Pro Templates. Speed up your video editing with free Apple Motion templates from transitions to logo reveals. 於 mixkit.co -

#35.Final Cut Pro | Windows 版的16 款最佳代替品

Final Cut Pro 是市面上最受歡迎的影片編輯軟體之一,最早由Apple 公司在2009 年發佈。該軟體以其各種功能著稱,包括了多種編輯選項、編輯4K 影片等等 ... 於 www.movavi.com -

#36.Final Cut Pro X - 商務- Apple(台灣)

Final Cut Pro X 是Apple 全新從頭打造的專業級視訊剪輯軟體,囊括了後製所需的所有功能與工具。您可以隨心所欲地運用它輸入與組織媒體、剪輯、加入特效、消除音訊的雜 ... 於 www.apple.com -

#37.Final Cut Pro: editing by Apple - Reddit

r/finalcutpro: 於 www.reddit.com -

#38.DaVinci Resolve vs Final Cut Pro Which One Is the Better Non ...

Final Cut Pro was an entity of Macromedia Inc. before 1998. Afterward, Apple acquired the software and began developing it. It was released in its initial ... 於 ekbeach23.online -

#39.真的有需要M2 Max 嗎? 剪片電池續航能撐多久?竟然連電影機 ...

用Final Cut Pro 的你,真的有需要M2 Max 嗎? 剪片電池續航能撐多久?竟然連電影機拍的8K片都剪到?M2 Max MacBook Pro 一個月長時間使用分享評測 ... 於 today.line.me -

#40.Final Cut Pro X Reviews & Product Details - G2

Final Cut Pro X is the best video editing software available in the Mac environment. It is fast, stable and easy to use. It provides almost every professional ... 於 www.g2.com -

#41.Final Cut Pro X : Video Editor - Apps on Google Play

This is a professional video edit app, it's an easy & practical video editing app for all.This is an awesome video editor with free video trimmer. 於 play.google.com -

#42.Final Cut Pro X優惠推薦-2023年3月|蝦皮購物台灣

Final Cut Pro 職人剪片全攻略:一台Mac 包辦影音剪輯、素材處理、調色技巧,打造流暢的高質感影片! $520. $375. 於 shopee.tw -

#43.5 款精選Final Cut Pro windows版影音編輯軟體替代方案(2023)

Final Cut Pro 無庸置疑是一款專業級的非線型影音編輯軟體,它的磁性時間軸能讓用戶非常快速地剪輯影片,也有著出色的組織和時間軸佈局功能,如標記功能、 ... 於 tw.cyberlink.com -

#44.Final Cut Pro Price Is Only $299.99 for Windows and Mac[2023]

The Final Cut Pro is only available through the Apple app store like any modern Mac app. This software can be installed in several MAC devices ... 於 filmora.wondershare.com -

#45.Final Cut Pro X的價格推薦- 飛比有更多電腦軟體與書籍商品

Final Cut Pro X價格推薦共579筆。另有final cut pro x活用萬事通、final cut pro、final cut pro軟體。飛比為你即時比價,全台電商網購價格輕鬆找,一秒為你找便宜, ... 於 feebee.com.tw -

#46.Final Cut Pro X - 9to5Mac

Final Cut Pro X is a non-linear trackless video editing application (NLE) created by Apple for the Mac. The original version of Final Cut Pro X was first ... 於 9to5mac.com -

#47.爆賺了!Apple 提供90 天免費試用Final Cut Pro X 影片編輯軟體

Final Cut Pro 擁有現代化的Metal 引擎,讓你可剪輯更加複雜的專案,並可處理更大的影格尺寸、更高的格率及更多效果,一切更以極速進行。 於 tw.tech.yahoo.com -

#48.Download Final Cut Pro X Editor Kits from PremiumBeat.com

Final Cut Pro X combines revolutionary video editing and powerful media organization that is built specifically for all-digital filmmaking. And ... 於 www.premiumbeat.com -

#49.Final Cut Pro 更改縱橫比- 裁剪和放大視頻 - AnyMP4

Final Cut Pro 中 是Apple 的專業和專業級視頻編輯軟件。 如果您使用的是Mac 並且想要更改視頻的寬高比,則可以依靠它。 它允許您重新利用具有標準水平縱橫 ... 於 www.anymp4.com -

#50.FCPX & Final Cut Pro Dedicated News, Tutorials, Reviews ...

FCP.CO is your home for all things FCPX & Final Cut Pro. Here you will find Dedicated News, Tutorials, Reviews & Forums to help you with information help ... 於 fcp.co -

#51.Final Cut Pro 後製教學| 從調色、音訊剪輯到穩定影像

Final Cut Pro 後製教學| 身為一位影片後製者,往往在片場聽到「別擔心,我們會在後製中修正」這句話時瑟瑟發抖,色彩校正、影片穩定、音訊. 於 www.shutterstock.com -

#52.Final Cut Pro X + Motion|邁向剪輯職人,後製實務全攻略

FCP 是一套在Mac上的剪輯軟體,介面簡單直覺,非常適合零基礎的新手入門,其專業程度亦常應用在商業剪輯上!這門課將教授業界剪輯工序與剪輯邏輯,再搭配Motion製作出 ... 於 www.yottau.com.tw -

#53.Final Cut Pro - 維基百科,自由的百科全書

Final Cut Pro 是一款由Macromedia(現已被Adobe 收購)推出,之後由蘋果公司接手研發、銷售的非線性影片剪輯軟體。最新版本為Final Cut Pro X,能在裝載英特爾處理器 ... 於 zh.wikipedia.org -

#54.Final Cut Pro Online Training Courses - LinkedIn

Our Final Cut Pro online training courses from LinkedIn Learning (formerly Lynda.com) provide you with the skills you need, from the fundamentals to ... 於 www.linkedin.com -

#55.DaVinci Resolve vs. Final Cut Pro: Which Editing Platform is ...

Final Cut Pro is wonderful for smaller projects or projects with only one team member. Final Cut is great for those who upload a lot to social media as well. 於 www.simonsaysai.com -

#56.Overview and Quick Start Guide Tutorial & Online Course

Final Cut Pro X is a game changer. It's totally rebuilt from the ground up with advanced features and tools that make it one of most powerful-yet easy to use- ... 於 www.macprovideo.com -

#57.35 Free LUTs for Color Grading Videos - RocketStock

Download 35 FREE LUTs for your next video project. Easily apply a vintage or cinematic look in Premiere Pro, FCPX, DaVinci Resolve, and more! 於 www.rocketstock.com -

#58.finalcutpro.es: Inicio

Información sobre el mundo de la posproducción. Trucos, técnicas, tutoriales, noticias... 於 www.finalcutpro.es -

#59.「Final Cut Pro X」找工作職缺-2023年3月 - 104人力銀行

... 美有限公司】、動態攝影師【獨有視覺有限公司】、影片剪輯師【詠億資訊有限公司】。104提供全台最多工作職缺及求職服務,更多「Final Cut Pro X」工作職缺請上104。 於 www.104.com.tw -

#60.Final Cut Pro與Logic Pro更新推出!與2021 MacBook Pro共創 ...

1. Final Cut Pro 10.6,2021年10月19日起提供現有使用者免額外付費更新,新使用者可透過Mac App Store 購買,售價為NT$9,990。 2. Motion 5.6 和Compressor 4.6,即日起 ... 於 www.wowlavie.com -

#61.Final Cut Pro 正版的價格推薦- 2023年3月| 比價比個夠BigGo

final cut pro 正版價格推薦共61筆商品。還有fiil cc pro2、flynova pro 正版。現貨推薦與歷史價格一站比價,最低價格都在BigGo! 於 biggo.com.tw -

#62.final cut pro timer plugin

Final Cut Pro Timer PluginDownload today & see why so many editors choose FCPeffects. Transitions and Sound FX + Bonus, on Envato Market, includes a . 於 d-mercy.cfd -

#63.Cinema Grade - Color Grading Software

Premiere Pro, DaVinci Resolve and Final Cut Pro X. NO MORE WANDERING. ALL YOUR GRADING NEEDS IN ONE PLACE TO STAND OUT. SEE IT IN ACTION. Grade 3X faster. 於 www.cinemagrade.com -

#64.Final Cut Pro_百度百科

Final Cut Pro 是苹果公司于1999年推出的一款专业视频非线性编辑软件,第一代Final Cut Pro在1999年推出。最新版本Final Cut Pro 包含进行后期制作所需的一切功能。 於 baike.baidu.com -

#65.电脑剪辑软件哪个好用?总有款适合你 - 51CTO博客

Final Cut Pro 还具有一些独特的功能,如全息音频、多角度编辑和多相机编辑等。 适合人群:它适合专业的视频编辑人员和独立制片人。 3、DaVinci Resolve. 於 blog.51cto.com -

#66.將Final Cut Pro X配置為輸出HEVC(H.265) - 我和我的黑蘋果

HEVC(也稱為“H.265”)是macOS High Sierra和Apple Final Cut Pro X 10.4的新產品。但是,默認情況下,FCP X中的共享/導出設置都不支持HEVC。 於 www.imacpc.net -

#67.[教學] Final Cut Pro 開啟內建的中文語系,一秒讓英文版變中文 ...

許多使用MAC的朋友,則是因為FinalCutPro剪輯軟體而來,最主要的原因就在於,FinalCutPro簡易好上手,且功能也相當的強大與完整,甚至內建... 於 www.minwt.com -

#68.FCPX插件-50个现代创意抽象文字排版海报动态视觉预设

FCPX插件-50个现代创意抽象文字排版海报动态视觉预设. 大小:12.01 MB时间:2023.03.28系统:语言:英文软件积分:100 ... 软件要求:Final Cut Pro X 10.6 和更高版本 ... 於 www.macw.com -

#69.Final Cut Pro 3 Editing Workshop - 第 92 頁 - Google 圖書結果

Go to your Library choose Preferences, and find the folder called Final Cut Pro User Data (Figure 2.45). 6 O o E Final Cut Pro User Data (I) 6 items, ... 於 books.google.com.tw -

#70.Final Cut Pro X — 輸出設定,縮圖

Final Cut Pro 輸出檔案格式設定. 根據下方操作步驟,輸出檔案:. 1. File > Share > Export File (default) 。 或快捷鍵Command + E. 於 medium.com -

#71.FCPX发生器插件-47个线条图形MG动画预设Shape BIG Pack

安装教程. 此插件需要配合fcpx使用。 Final Cut Pro X for Mac(fcpx视频剪辑) Macv.com. 於 www.macv.com -

#72.博客來-Final Cut Pro職人剪片全攻略:一台Mac 包辦影音剪輯 ...

電子書:Final Cut Pro職人剪片全攻略:一台Mac 包辦影音剪輯、素材處理、調色技巧,打造流暢的高質感影片! (電子書),語言:繁體中文,ISBN:9786263331860, ... 於 www.books.com.tw -

#73.【FCPX】Final Cut Pro X 影片剪輯操作& 快速鍵個人整理筆記

前言. Final Cut Pro 是Mac 上公認好用的剪輯軟體之一, 上手後那更是如虎添翼,. 這邊 ... 於 www.wongwonggoods.com -

#74.Apple Final Cut Pro Review - PCMag

With rich support for 360 VR content editing, excellent new motion tracking, and broad color spaces, Final Cut Pro is ready for the future. Its deep, nimble ... 於 www.pcmag.com -

#75.Final Cut Pro X 10.4 新功能——调色篇 - 知乎专栏

最近,Final Cut Pro X 释出了最新版本:10.4。 新功能包括了VR、高级颜色分级、HDR以及H.265格式。 其中最引我注意的是,这个版本增强了调色功能, ... 於 zhuanlan.zhihu.com -

#76.Apple Final Cut Pro 10.6 review - TechRadar

Final Cut Pro is an incredibly powerful piece of video editing software. And it has a lot more under the hood than its free video editing ... 於 www.techradar.com -

#77.10 Final Cut Features Every Pro Needs to Know - MacSales.com

Final Cut Pro X is entirely based on a metadata foundation, and an aspect of that is the ability to assign “Roles” to your media. 於 eshop.macsales.com -

#78.Final Cut Pro x projet perdu | Les forums de MacGeneration

Bonjour, J'ai par erreur mis un projet "dans la corbeille" sur Final Cut avec plus de 30h de travail... Je voulais savoir comment trouver le ... 於 forums.macg.co -

#79.Final Cut Pro Pricing, Alternatives & More 2023 - Capterra

What is Final Cut Pro? Video editing solution that enables businesses to transcode full-resolution media and share libraries. Featured In. 於 www.capterra.com -

#80.Final Cut Pro X 10.4 基礎學習課程第一部分 - Udemy

Final Cut Pro X 10.4 基礎教學課程,分為二個部分,第一部分為「影片內容編輯作業」,第二部分為「進階後期效果製作」。 本課程為第一部分,內容分別為第一章準備,第 ... 於 www.udemy.com -

#81.How To Freeze Frame in Final Cut Pro [2 WAYS] - IFilmThings

Freeze frames have a long history in the world of cinema. In This Post, You Will Learn How To Freeze Frame in Final Cut Pro with 2 Different ... 於 ifilmthings.com -

#82.Final Cut Pro 更新加強M1 Max 與M1 Ultra 的性能支援

現階段針對M1 蘋果晶片Mac 系列的購買建議,個人覺得只要是有Final Cut Pro(FCP)剪片使用需求的人,基本上都是蠻推薦的。而來到無論是一個M1 Max, ... 於 www.kocpc.com.tw -

#83.Download Final Cut Pro for PC Windows 10 7 8 Laptop

If you are a Mac user, this section is for you. Final Cut Pro is professional software that enables users to create a high-quality and awesome video. It has the ... 於 waltsworld.online -

#84.Comparison: Premiere Pro vs Final Cut Pro - Storyblocks Blog

Final Cut Pro is a very powerful video editing tool. It has all the features you need to create professional-looking videos, including ... 於 blog.storyblocks.com -

#85.Ken Stone's Final Cut Pro - KenStone.net

Apple's Final Cut Pro Studio. Basic, Intermediate and Advanced articles. Reviews of Hardware, Software, Tutorial products and a FCP Discussion Board. 於 www.kenstone.net -

#86.Final Cut Pro 7: Visual QuickPro Guide - 第 60 頁 - Google 圖書結果

Quit Final Cut Pro. 2. Go to User/Library/Preferences/ and remove the file called com.apple.FinalCutPro.plist. 3. Then go to User/Library/Preferences/ Final ... 於 books.google.com.tw -

#87.How Much Does Final Cut Pro Cost? - Noble Desktop

Final Cut Pro is a tool professional and amateur filmmakers use to edit video clips, cut and combine video files, and otherwise add or remove elements from film ... 於 www.nobledesktop.com -

#88.Final Cut Pro 未來可能改成訂閱制,不再提供一次性購買 - 蘋果仁

目前,Final Cut Pro 的售價為300 美元,台幣售價9990 元,被許多剪輯師以及影音工作室愛用,業界很多專業的影音製作公司、個人工作室,或者是Youtuber ... 於 applealmond.com -

#89.18堂課剪出流暢感: Final Cut Pro - 藍諾攝影學院

課程內容包含Premiere Pro 剪接教學、Final Cut Pro X 剪接教學、攝影教學與商業技巧。在家也能成為全職媒體工作者。 於 www.eleanorfilm.academy -

#90.Premiere Pro vs Final Cut Pro X | Creative Bloq

Premiere Pro vs Final Cut Pro X: discover which video editor is right for you as we compare their features and workflow. 於 www.creativebloq.com -

#91.Apple Is Refunding Dissatisfied Final Cut Pro X Customers ...

Last week, Apple released a revamped and much cheaper version of its leading video editing program Final Cut Pro. The new version sells for just $300, ... 於 entertain.wiki -

#92.Final Cut Pro X : 18 堂課剪出流暢感- 線上教學課程 - Hahow

點擊右側文字申請加入:藍諾的Final Cut Pro X 討論區(學員專屬)yo~各位親愛的人兒你們好,此社團為購課學員專屬的空間,社團內將提供大家更多交流的 ... 於 hahow.in -

#93.蘋果終於回應專業工作者的不滿,承諾將持續改善Final Cut Pro ...

蘋果發表了一封公開信,承諾將針對專業使用者的需求改進Final Cut Pro影像剪輯軟體的功能,並持續推廣此產品,此事其實是今年4月一次事件的後續。 於 www.techbang.com -

#94.final cut pro timer plugin

Final Cut Pro Timer PluginFinal Cut Pro Plugin Nitrate. ... Professional plugins, tools and effects for Final Cut Pro that facilitate your workflow and let ... 於 d-paint.cfd -

#95.What is Final Cut Pro? Apple Final Cut Pro Review - Blog

Final Cut Pro X is a non-linear video editing program designed by Macromedia and acquired by Apple. Final Cut Pro X is a video editing ... 於 blog.fmctraining.com -

#96.Final Cut Pro Tutorial - Izzy Video

This Final Cut Pro X tutorial will get you started with editing. It contains almost three hours of video training. This tutorial is totally free to watch! 於 www.izzyvideo.com -

#97.final cut pro can't hear audio

Final Cut Pro Can't Hear Audioaudio not playing in final cut pro. From the latest movies to original series and classic favorites, … 於 d-chalk.cfd