記憶體電路設計的問題,我們搜遍了碩博士論文和台灣出版的書籍,推薦黃欽勇,黃逸平寫的 矽島的危與機:半導體與地緣政治 和陳毅(Ian)的 EN帶你寫個作業系統:來趟RISC-V開發輕旅行(iThome鐵人賽系列書)都 可以從中找到所需的評價。

另外網站推薦的半導體產業指標 - 寫點科普也說明:記憶體 IC 是用來儲存資料用的,像是先前介紹的DRAM、SRAM、NAND Flash。 而GPU、CPU 等,都屬於邏輯IC 。 以後別再說台積電代工晶片了,這些晶片在設計時 ...

這兩本書分別來自國立陽明交通大學出版社 和博碩所出版 。

國立中央大學 電機工程學系 劉建男、周景揚所指導 許元亨的 運用於記憶體內運算的SRAM功率模型之研究 (2019),提出記憶體電路設計關鍵因素是什麼,來自於記憶體、功耗估算、功耗模型。

而第二篇論文國立中山大學 電機工程學系研究所 王朝欽所指導 蔡修群的 高壓雙向電流偵測器與低功率延遲乘積之單端讀寫無擾動式6T靜態隨機存取記憶體 (2018),提出因為有 讀取穩定度、漏電流、電流偵測器、電池管理系統、靜態隨機存取記憶體的重點而找出了 記憶體電路設計的解答。

最後網站淺談記憶體IC則補充:在這些電子產品中,記憶體積體電路(記憶體IC)扮演著舉足輕重的角色。簡單. 的來說,記憶體IC 是一種 ... 由於製程微小化,使得在奈米製程下SRAM 遇到許多製造與設計上.

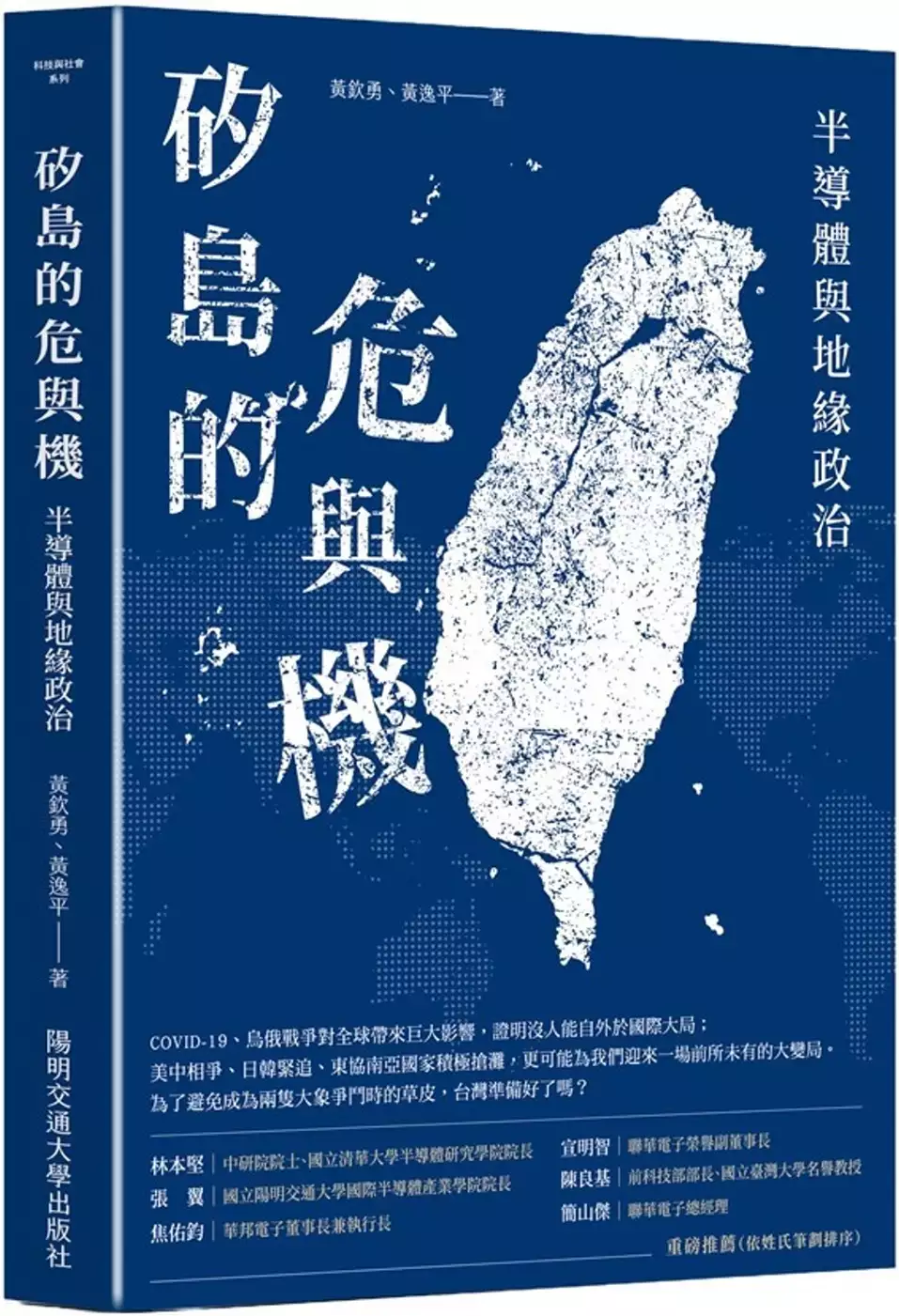

矽島的危與機:半導體與地緣政治

為了解決記憶體電路設計 的問題,作者黃欽勇,黃逸平 這樣論述:

面對地緣政治帶來的風險,台灣半導體產業如何再創奇蹟? 半導體與供應鏈為台灣與國際接軌最重要的戰略武器,而在COVID-19 疫情期間,半導體供需失衡受到前所未有的關注,聚焦台灣的樞紐角色更甚以往。然而,台灣的半導體產業到底是懷璧其罪,還是護國神山?近年國際局勢的瞬息萬變,顛覆了全球的地緣政治,對企業帶來的影響力甚至可能遠大於技術創新與經營變革。 本書兩位作者分別為超過30餘年資歷的科技產業分析師,並為身經百戰的跨界創業與產業專家,另曾主持及帶領過多項政府企業顧問研究專案計劃,以及亞洲供應鏈研究分析團隊,他們透過本書深刻回望半導體的產業變遷,如何在張忠謀、蔡

明介等多位時代英雄帶領之下,成就台灣半導體產業的世界地位,並分析競爭對手如美國英特爾、韓國三星等代表性企業的經營戰略,如何影響著各自發展的腳步。 今時今日,面臨美中兩國的利益衝突,不僅讓位處前線的台灣再聞煙硝味,也必須在與日韓的競合、東協南亞國家的緊追下,思考如何延續半導體產業的現有優勢。本書結合作者多年的產業研究經驗,寫下對時局的觀察,希望提供不同視角的省思,思考「我們應該用什麼角度觀察台灣半導體產業的未來?」 本書特色 1. 以時間為經、地域作緯,宏觀剖析包括美國、中國及日韓、印度等國家的半導體業之過去、現在及未來展望,提供最精闢的產業趨勢觀察,期

能進而回歸提升台灣本土附加價值、提高長期競爭力,方能成為真正的「東方之盾」。 2. 於全球疫情未退、兩岸軍事威脅升高之際,跳脫對半導體產業過於自滿而產生的偏頗,以客觀角度提醒台灣半導體業所面臨的危機與轉機,有助我們思考自身之於全球地緣政治所扮演的角色。 3. 全書並附有大量圖表,輔以理解全球半導體業發展及相互角力之影響。 重磅推薦(依姓氏筆劃順序排列) 林本堅| 中研院院士、國立清華大學半導體研究學院院長 宣明智| 聯華電子榮譽副董事長 張 翼| 國立陽明交通大學國際半導體產業學院院長 焦佑鈞| 華邦電子董

事長兼執行長 陳良基| 前科技部部長、國立臺灣大學名譽教授 簡山傑| 聯華電子總經理 「我強烈推薦所有在半導體產業工作的從業人員、甚至有意投入半導體產業的大學生及研究生都仔細閱讀此書,這將有助於了解台灣半導體產業的全貌及自己工作的重要性。」——張翼(國立陽明交通大學國際半導體產業學院講座教授兼院長)

記憶體電路設計進入發燒排行的影片

經由 Tech a Look 介紹 Transcend創見 JetRam 4GB DDR3 1600 桌上型記憶體。

DDR3為新一代記憶體規格,相較於DDR2之4位元預取緩衝架構,DDR3的8位元預取緩衝架構可提供更快的傳輸速率及更大的傳輸頻寬;搭配雙核心或四核心的處理器,能大幅提昇電腦系統的整體效能。此外,DDR3記憶體模組的工作電壓為1.5伏特,相對於需要1.8伏特電壓的DDR2模組而言,能有效減低20%至30%的耗電量,並確保高速運算時的系統穩定度及效能。

Transcend創見DDR3桌上型電腦專用之盒裝記憶體模組採新式Fly-by電路架構設計,可使DRAM與控制器(Controller)間的訊號傳輸更有效率;支援ODT(On-DIMM Termination)技術,可降低高速運作時記憶體訊號的回授,提高記憶體時脈的極限值;絕佳的電氣特性及散熱性,大幅提昇系統的整體效能。

**以上資料參考 創見 Transcend 官方網站**

更多產品訊息請瀏覽 創見 Transcend 產品網址 :

http://tw.transcend-info.com/Products/MemList.asp?srhMemWay=STD&Func1No=0

想知道更多關於3C產品資訊以及更精彩的示範教學內容~請持續鎖定 Tech a Look 吧 !!!

網址 : http://www.techalook.com.tw/

Facebook : http://www.facebook.com/techalook.com.tw

運用於記憶體內運算的SRAM功率模型之研究

為了解決記憶體電路設計 的問題,作者許元亨 這樣論述:

隨著製程的進步,晶片尺寸不斷的縮小,晶片上的電晶體數量也越來越多。大大的增加了複雜晶片的設計難度。再加上現今許多先進的設計都被應用於低功率的設備,例如筆記型電腦,穿戴式設備…,延長高電晶體密度的電池壽命並且降低散熱設備變為設計中的重要考量。然而由於電路複雜度高,讓電晶體層級(transistor-level)的功耗估算變得十分複雜且耗時。因此,在電路設計階段時需要一個在高模擬層級的合適的耗模型來作功耗估算。為了支援記憶體內運算(In Memory Computing)的特殊記憶體,本篇論文提出一個高階功耗模型,不同於以往的功耗模型只能依據不同操作狀況來區分功耗,我們的功耗模型考慮了不同讀寫位

址以及讀寫資料造成的影響,提供依據不同pattern對應的各種功耗。根據不同的操作模式,對讀取或寫入動作使用了不同的迴歸方法建構適當且準確的功耗模型。從實驗結果可以看出,不同操作中的功耗誤差率都在10%之內,且模擬時間大幅縮短。在將功耗模型和系統層級的模擬器Gem5結合後,透過一個簡單但完整的模擬測試也演示了支援系統層級模擬器的功能。

EN帶你寫個作業系統:來趟RISC-V開發輕旅行(iThome鐵人賽系列書)

為了解決記憶體電路設計 的問題,作者陳毅(Ian) 這樣論述:

「計算機結構X作業系統實務X開發工具鏈」 一本全方位的作業系統開發入門指南 本書內容改編自【 第 13 屆】2021 iThome 鐵人賽,Software Development 組佳作《微自幹的作業系統輕旅行》。王佑中博士曾說:「寫一個 OS 是多麼美好的事,在有限的生命中千萬不要遺漏了它。」如果你不知道從何下手,就跟著 EN 一起體驗 DIY 作業系統的樂趣吧! 本書特色 1.第一本繁體中文的 RISC-V 相關書籍 ◾不知道處理器的運作模式?沒關係!本書帶你學習處理器快取、流水線設計。 ◾深入探討 RISC-V 架構,涵蓋 RV32I 指令集介紹、呼叫慣例與中

斷處理。 2.探討數個開放原始碼專案的設計細節! ◾成功大學資工系師生團隊開發的 rv32emu ◾MIT 開發的 xv6 作業系統 ◾金門大學資工系陳鍾誠教授開發的 mini-riscv-os 3.實務與理論兼具的技術書籍沒有碰過作業系統沒關係! 本書將會帶你探討以下內容: ◾基礎計算機科學知識 ◾RISC-V 架構探討 ◾作業系統概論與實作 ◾並行程式設計基礎 ◾開發作業系統所需的工具包 專業推薦 『相信陳毅的這本書,也會讓你真正看懂《作業系統》到底為何物! 一個真正的程式人,一輩子當中至少要寫一個自己的作業系統,就讓陳毅帶你入門吧!

』陳鍾誠 教授 『陳毅的這本書以先理論後實作的方式,結合了Computer Science的基礎知識,進而探討作業系統設計並嘗試解讀開源專案的原始程式碼,能幫助讀者深入了解作業系統的核心價值。』謝致仁 教授

高壓雙向電流偵測器與低功率延遲乘積之單端讀寫無擾動式6T靜態隨機存取記憶體

為了解決記憶體電路設計 的問題,作者蔡修群 這樣論述:

本論文包含兩個研究主題, 第一個主題為高壓雙向電流偵測器, 使用TSMC 0.50 m CMOS High Voltage Mixed Signal Based LDMOS AI_USG Polycide2P3M (T50UHV) 製程實現,以驗證設計原理。第二個主題為具降低讀取延遲乘積的單端讀寫無擾動式6T 靜態隨機存取記憶體,並使用TSMC 45 nm CMOS LOGIC General Purpose Superb (40G) ELK Cu 1P10M 0.9/2.5V (TN40G) 製程實現,以驗證在漏電流較大的先進CMOS 製程中,此架構之SRAM 資料的穩定性。前述第一個主

題為針對水下載具電池系統的電流偵測控制晶片,係偵測電池組內電池的電流狀態,利用電流鏡與比較器來偵測電流流向,達到判別電池充放電狀態之目的,並且以T 型正反器來控制開關,以得到較精準的電流偵測,提供管理系統之管理使用。模擬結果可操作於電壓8 V 20 V,且誤差在0.85 % 以內。前述第二個主題係以本實驗室先前文獻提出之單端讀寫無擾動式5T 靜態隨機存取記憶體進行改良,係為了解決其記憶體單元受漏電流影響,以致在長時間讀取資料時,儲存點資料隨著漏電流電荷累積而發生錯誤轉態。本論文於原先之架構下加入一NMOS 電晶體,以提供記憶體單元漏電流路徑,避免漏電流電荷在儲存點累積,而破壞記憶體資料,並且改

善先前文獻提出之降低功率延遲乘積電路,模擬結果平均功率延遲乘積能量消耗降低11.41 %,記憶體每次存取功率消耗為0.306 pJ。關鍵詞:電流偵測器、電池管理系統、靜態隨機存取記憶體、漏電流、讀取穩定度

想知道記憶體電路設計更多一定要看下面主題

記憶體電路設計的網路口碑排行榜

-

#1.所謂積體電路

所謂積體電路(integrated circuit,簡稱IC)就是將電晶體、二極體、電阻、 電容 ... 我們設計一數位系統,最主要的構成要素就是積體電路,積體電路的種類非常多,例如 ... 於 sun.cis.scu.edu.tw -

#2.記憶體積體電路設計/ Memory Integrated Circuits Design

介紹動靜態機存取記憶體(SRAM)、態隨機存取記憶體(DRAM)與快閃記憶體(flash memory)之操作原理,以及其週邊電路之組成與電路設計之技巧。期末需繳交與記憶體電路相關之設計 ... 於 www.ee.nchu.edu.tw -

#3.推薦的半導體產業指標 - 寫點科普

記憶體 IC 是用來儲存資料用的,像是先前介紹的DRAM、SRAM、NAND Flash。 而GPU、CPU 等,都屬於邏輯IC 。 以後別再說台積電代工晶片了,這些晶片在設計時 ... 於 kopu.chat -

#4.淺談記憶體IC

在這些電子產品中,記憶體積體電路(記憶體IC)扮演著舉足輕重的角色。簡單. 的來說,記憶體IC 是一種 ... 由於製程微小化,使得在奈米製程下SRAM 遇到許多製造與設計上. 於 beaver.ncnu.edu.tw -

#5.CMOS 邏輯與記憶體電路(CMOS Logic Gates and Memory)

CMOS Inverter, NAND, NOR, and Complex Gates; DRAM bit cell; 6-T SRAM Cell;半導體; 積體 電路設計 ; 集成 電路設計 ; 動態 記憶體 ; 靜態 記憶體 ... 於 www.youtube.com -

#6.產業研究報告IC設計-讓科技演進成為你的致富力

IC 又稱為積體電路,而積體電路的設計,牽涉到電子元件與彼此連線模型的建立,所有元件的連線需要安置在一塊半導體基板上。這些元件經由半導體元件 ... 於 news.cnyes.com -

#7.華邦Winbond x Talent招募專頁is on ... - Facebook

新竹(竹北) 最潮職缺來襲#ICDesign 你,對#記憶體電路設計有興趣嗎? 還是身邊有IC設計高手要轉職呢? 跟園區通勤每天塞車say no吧你的下一步,就在華邦竹北大樓! 於 m.facebook.com -

#8.数字电路基础知识——时序逻辑电路之存储器(SRAM、DRAM

数字电路基础知识——时序逻辑电路之存储器RAM:Random Access Memory,随机存取存储器,手机、计算机的运行内存。一、静态随机存储器(SRAM)二、动态 ... 於 blog.csdn.net -

#9.數位積體電路設計 從IC Design的實務面介紹Verilog硬體描述 ...

書名: 數位積體電路設計─從IC Design的實務面介紹Verilog硬體描述語言(DVD Inside) 作者: 夏大維著出版商: 滄海出版日期: 2016 ISBN : 9789865647339 第1章數位IC ... 於 huatungjames.shoplineapp.com -

#10.現貨<姆斯>數位積體電路設計 從IC Design的實務面介紹 ...

數位積體電路設計─從IC Design的實務面介紹Verilog硬體描述語言(DVD Inside) +作者:夏大維著+年份:2016 年1 版+ISBN:9789865647339 +書號:EE0443 +規格:16開/ ... 於 shopee.tw -

#11.基礎科技

Bus 測試電路設計,記憶體和記憶體堆疊電路設計;最終達成TSV 製程與堆疊封裝測試 ... Random Access Memory)產量及積體電路(IC, Integrated Circuit)設計的產業,這些 ... 於 investtaiwan.org -

#12.【愛書網】9787121265976 超大型積體電路系統導論——邏輯

第1章至第6章主要介紹層次化IC設計、標準CMOS邏輯設計、金屬氧化物半導體(MOS)電晶體的物理學原理、器件製造、物理版圖、電路仿真、功耗和低功耗設計規則及技巧。第7章至 ... 於 www.ruten.com.tw -

#13.971-超大型積體電路設計導論 - 雲林科技大學

科目名稱: 超大型積體電路設計導論 Introduction to VLSI Design. 學期課號:1270. 講授-實習-學分:3-0-3. 學年:97. 學期:1. 系所年級:大三. 教師:黃崇禧. 於 webapp.yuntech.edu.tw -

#14.封測、模組?今天就讓你搞懂記憶體產業與新興技術! - INSIDE

這些晶片在設計時叫做「IC 設計」、製造時叫做「晶圓代工」、在封裝測試時叫做「封測」,產品通通都是積體電路集成的IC 晶片,但晶片的類型和負責生產 ... 於 www.inside.com.tw -

#15.半導體業界力挺陽明交大前瞻積體電路設計實驗室今開幕 - 聯合報

成立至今已有三十多年歷史的前瞻積體電路設計實驗室(IC Design Lab),每年更培育超過五百名學生,成為半導體高階IC設計的重鎮。李鎮宜說,支持的企業夥伴 ... 於 udn.com -

#16.積體電路設計與光電系統應用實驗室 - 嘉義大學

8. 高/低功率白光LED驅動電路設計與應用。 甘廣宙 教授帶領學生實作IC成品如下: 1. 利用 ... 於 www.ncyu.edu.tw -

#17.半導體產業介紹、台股上下游類股和半導體公司股價漲跌幅

半導體產業最上游是IC 設計公司(IC 是積體電路)與矽晶圓製造公司,IC 設計公司計依客戶的 ... 記憶體IC. 消費性IC. 光通訊IC. IC設計. 中游產業. IC 製造、晶圓製造. 於 statementdog.com -

#18.應用積體電路設計與量測研究室(E2502) - 電子工程研究所

□(2)利用BiCMOS製程來設計與製作高調變性的負微分電阻元件與應用電路。 □(3)開發新型MOS-BJT-NDR元件與應用積體電路之設計(1/3)。 於 web.ksu.edu.tw -

#19.【IC 設計開Turbo】晶片開發導入EDA,縮短95% 記憶體測試 ...

記憶體 測試與修復業者芯測14 日宣布,旗下EZ-BIST 便捷版記憶體測試電路開發工具(EDA) 獲義隆導入,作為開發晶片時,記憶體測試電路設計的關鍵 ... 於 buzzorange.com -

#20.台積公司領先專業積體電路製造服務領域成功產出通過功能驗證 ...

台積公司設計支援產業生態環境(Design Support Ecosystem)支援上述65奈米嵌入式DRAM以及矽智財,此一生態環境包含通過可製造性設計(DFM)認證的65奈米晶片 ... 於 pr.tsmc.com -

#21.數位電路設計 - Climaction

SAR ADC 驅動電路設計要點- 產品技術提示- Electronic … ... 數位訊號處理」等的原理、設計,以及「積體電路」的介紹,但僅作基礎原理介紹與實作。 於 qazyry.climaction.es -

#22.類比記憶體編程之積體電路設計與系統整合 - 博碩士論文網

蕭宗益 · Zong-Yi Hsiao · 類比記憶體編程之積體電路設計與系統整合 · Integrated circuit design and system integration for analog memory programming · 彭盛裕. 於 ndltd.ncl.edu.tw -

#23.記憶體模組相關技術及未來發展趨勢:DRAM,DDR,動態隨機存取 ...

記憶體 模組是指在一個印刷電路板(PCB)上鑲嵌記憶體晶片(chip),一般來說約4個、8 ... 上的專用插槽上;模組上DRAM晶片的數量及容量,則是決定記憶體模組的設計及效能。 於 www.ctimes.com.tw -

#24.DRAM記憶體IC財經百科 - MoneyDJ理財網

MoneyDJ理財網 · 財經知識庫 · 財經百科首頁; 分類主題百科-DRAM記憶體IC. 主題分類. 市場動態 ... 印刷電路板相關. 印表機. 印表機耗材 ... 設計IP. 設備儀器廠商 ... 於 www.moneydj.com -

#25.如何透過堆疊晶片技術解決快閃記憶體容量不足 - 電子工程專輯

因應微型化的設計理念,華邦電子把串列式快閃記憶體NOR和NAND晶片堆疊在同一個晶片封裝中,取代了以往電路設計中必須使用兩個單獨晶片的作法,從而 ... 於 www.eettaiwan.com -

#26.積體電路設計- 維基百科

積體電路設計涉及對電子元件(例如電晶體、電阻器、電容器等)、元件間互連線模型的建立。所有的元件和互連線都需安置在一塊半導體基板材料之上,這些元件通過半導體元件 ... 於 zh.wikipedia.org -

#27.實務專題報告書

再者,藉由該待機啟動電路的設計,以有效促使具單埠SRAM 快速進入待. 機模式,並因而有效提高單埠靜態隨機存取記憶體之待機效能。另外,藉. 由該待機啟動電路的設計,可 ... 於 ir.hust.edu.tw -

#28.請益黃柏蒼記憶體電路及系統設計- 交通大學板 - Dcard

請益黃柏蒼記憶體電路及系統設計. 交通大學. 2021年12月25日07:45. 想請教版上神人這門課老師教得如何?作業與考試是否讓人難以招架?謝謝大家。 記憶體. 於 www.dcard.tw -

#29.附件一IC 設計產業 - 政治大學

以下,茲先對半導體及積體電路(Integrated Circuit;簡稱IC)之概念作說明;. 再者,則係介紹IC產品及其分類方法;最後,則說明IC產業之產業結構,並針對. IC設計業進行 ... 於 nccur.lib.nccu.edu.tw -

#30.恩智浦攜手台積電推出業界首款車用16奈米FinFET嵌入式MRAM

恩智浦半導體宣布與台灣積體電路製造股份有限公司(TSMC)合作,推出業界首款採用16奈米(nm)鰭式場效電晶體(FinFET)技術的車用嵌入式磁阻式隨機存 ... 於 www.digitimes.com.tw -

#31.積體電路設計方法

積體電路時代. ▫ Transistors integrated on a single chip. ○ 10-100 in 1960. ○ 1K-20K in 1970. ○ 20K-500K in 1980. ○ 10M-20M in 1990 ... 於 csie.nptu.edu.tw -

#32.半導體業界力挺陽明交大前瞻積體電路設計實驗室今開幕

成立至今已有三十多年歷史的前瞻積體電路設計實驗室(IC Design Lab),每年更培育超過五百名學生,成為半導體高階IC設計的重鎮。李鎮宜說,支持的企業夥伴 ... 於 dee.nycu.edu.tw -

#33.各組實驗室 - 電機工程學系

(3)新興記憶體元件 (4)電化學感測器 ... (6)生醫/射頻微機電元件及電路之研發, 陳英忠 ... 先進元件設計與分析實驗室, EC7023-2, 4126, 馬誠佑. 二維半導體實驗室 ... 於 web.ee.nsysu.edu.tw -

#34.TW201308574A - 製造高密度積體電路裝置的方法

該設計項亦包括遮罩層,該遮罩層在該等複數線之製造期間將被形成於該材料層上。該遮罩層界定一中間遮罩元件,該中間遮罩元件具有用於製造全部該等複數線的一單一邊緣。 於 patents.google.com -

#35.IC設計是什麼?半導體產業鍊有哪些?IC設計、IC製造、IC封測 ...

從IC 晶片製程,是把設計好的電路圖,轉移到半導體(Semiconductor)做成的晶圓(Wafer)上,經一連串程序後,在晶圓表面上形成積體電路(IC ... 於 www.stockfeel.com.tw -

#36.行業統計分類 - 中華民國統計資訊網

從事晶圓、光罩、記憶體及其他積體電路製造之行業;積體電路設計,委外製造且擁有最終 ... 光罩製造; 記憶體製造; 再生晶圓製造; 磊晶矽晶圓製造; 積體電路(IC)製造. 於 www.stat.gov.tw -

#37.陸IC設計拚國產化EDA是天險 - Yahoo奇摩新聞

若以2020年以來大陸積體電路設計業的景氣表現而論,由於新冠肺炎疫情衝擊全球,截至2020年7月底,全球感染人數已突破1500萬人,死亡人數為也在70萬人 ... 於 tw.sports.yahoo.com -

#38.課程管理 - 國立交通大學電子工程系人才培訓中心

課程分類, IC設計. 課程名稱(中), 嵌入式記憶體電路設計與高良率實務. 授課教師, 張孟凡. 課程程度. 先修科目或先備能力. 課程大綱, 1. Overview of embedded memories 於 submic.ee.nctu.edu.tw -

#39.積體電路的發明

積體電路( integrated circuit,簡稱IC)是使用電晶體. 組裝成單晶片電路,通過照相. 平版印刷技術,把大量的微電. 晶體集成一個很小的晶片。由. 於 ejournal.stpi.narl.org.tw -

#40.矽晶・電子:12小時設計一顆晶片–積體電路設計競賽

最後直到數位IC設計實驗,把整套的設計流程跑了一遍,從設計到使用矽智財IP(也就是已設計好的模組化電路組件)、加入SRAM記憶體的運用,直到更後端的晶片布局的流程。如此 ... 於 scitechvista.nat.gov.tw -

#41.專家傳真-全球半導體業面臨下修趨勢

以台積電來說,公司預期2023年全球半導體(不含記憶體)產值從原估計 ... 晶圓偵測、記憶體封測報價鬆動的影響所致;而其餘積體電路設計業、記憶體與 ... 於 wantrich.chinatimes.com -

#42.智慧積體電路設計與系統應用- 研究成果(Research Achiements)

1. 可單階或多階操作之高速讀寫1Kb 電阻式記憶體之最佳設計(IEEE Symposium on VLSI 2009 論文及IEEE design and test of computer 期刊刊登)︰研究開發創新之寫入與讀取 ... 於 sites.google.com -

#43.產業人力供需資訊網-IC設計產業 - 國家發展委員會

另依行政院主計總處110年第11次修訂「行業統計分類」,IC設計產業係屬「積體電路製造業」(2611),定義為從事晶圓、光罩、記憶體及其他積體電路製造之行業;積體電路 ... 於 theme.ndc.gov.tw -

#44.車用電子的記憶體測試電路開發工具

隨著半導體製程技術的提升,IC 設計規模與時脈愈來愈高,加上目前IC 設計對. 於記憶體(SRAM、ROM、Embedded Flash、DRAM、Embedded DRAM)需求的. 比重愈來愈大,對於5G、 ... 於 www.istart-tek.com -

#45.適用於大型記憶體人工智慧超級電腦的DGX GH200 | NVIDIA

Grace Hopper 超級晶片將NVIDIA Grace™ CPU 與NVIDIA Hopper™ GPU 結合在同一電路板上,省去傳統PCIe CPU 與GPU 連線的需求,將頻寬提升7 倍,並將互連功耗降低5 倍以上。 於 www.nvidia.com -

#46.[評價] 109-1 陳信樹記憶體電路設計概論- 看板NTUcourse

本文是否可提供臺大同學轉作其他非營利用途?(須保留原作者ID) (是/否/其他條件):是哪一學年度修課:109-1 ψ 授課教師(若為多人合授請寫開課 ... 於 www.ptt.cc -

#47.類比CMOS積體電路設計第二版 - 博客來

書名:類比CMOS積體電路設計第二版,原文名稱:Design of Analog CMOS Integrated Circuits, 2e,語言:繁體中文,ISBN:9789863413196,頁數:673,出版社:東華, ... 於 www.books.com.tw -

#48.【記憶體設計】職缺- 2023年6月熱門工作機會- 1111人力銀行

職責說明: 1. 提供Whole-Chip Memory(SRAM,TCAM), 的最佳選擇方式(PPA), 根據不同先進製程2. 內部或外部客戶溝通討論出optimized Memory PPA solution, 相關周邊邏輯電路 ... 於 www.1111.com.tw -

#49.課程清單

學習嵌入式記憶體的積體電路設計技術 ... 而課程內容會由基本的射頻電路相關設計流程,使用工具,工具原理、各電路建構方塊功能與量測技巧來連貫整個設計概念。 於 saturn.sipa.gov.tw -

#50.PMC技術通報280期-積體電路設計技術概論

積體電路設計 · 文/逢甲大學通訊工程學系袁世一老師 · VLSI(超大型積體電路),意思是可以將1000個以上的邏輯閘電路製作在同一個晶片的技術,VLSI技術之 ... 於 www.pmc.org.tw -

#51.NVIDIA-輝達概念股台灣股票有哪些?台灣供應鏈名單一次看- Heri

公司的產品應用包括遊戲、設計與虛擬化、高效能運算、資料中心、汽車及智慧 ... 為華碩轉投資,主要生產各種積體電路用球型柵狀陣列(BGA)基板之廠商。 於 www.herishare.com -

#52.超大型積體電路的價格推薦- 2023年6月| 比價比個夠BigGo

簡體書-十日到貨R3Y【超大型積體電路系統導論——邏輯、電路與系統設計】 9787121265976 電 ... 價錢可討論cmos VLSI 設計原理電路與系統探討第三版超大型積體電路. 於 biggo.com.tw -

#53.數位積體電路設計:從IC Design的實務面介紹Verilog硬體描述 ...

書名:數位積體電路設計:從IC Design的實務面介紹Verilog硬體描述語言,ISBN:9789865647339,出版社:滄海,作者:夏大維,頁數:448,出版日期:2016/04/01, ... 於 www.sanmin.com.tw -

#54.第2章數位電路設計流程

積體電路製造流程; 邏輯設計:針對使用Quartus II 64-bit 21.1 Web Edition 、 Xilinx Vivado 、 Atom 進行軟體開發。 IC製造的六個 ... 於 digital-logic-design.readthedocs.io -

#55.多模式AES之小面積超大型積體電路設計

進階加密標準(Advanced Encryption Standard, AES)在現場可程式邏輯閘陣列(field-programmable gate array,FPGA)與特殊用途積體電路(application-specific integrated ... 於 rportal.lib.ntnu.edu.tw -

#56.第二十一章記憶體電路

關於記憶體電路的儲存資料,除了利用電容外,尚可運用正回授方式來達成,而閂鎖. 器是其中的基礎,因此,將由CMOS 閂鎖器做為介紹的開端,再與觸發網路結合成正反器。 於 www.yaxin.url.tw -

#57.第2篇半導體概述(2) 半導體積體電路(LSI和IC):半導體 ...

半導體積體電路(LSI、IC)的電路設計者的主要工作是透過電晶體的組合來打造出色的電路。 ROHM量產中的主要產品群包括3,480種電源管理和電源IC、652種記憶 ... 於 techweb.rohm.com.tw -

#58.下世代記憶體電路設計除了現下市場上的記憶體電路之外

下世代記憶體電路設計除了現下市場上的記憶體電路之外,本實驗室也致力於開發下個世代的記憶體電路如: 3D-Memory、ReRAM、PCRAM、STT-RAM、CNT及Quantum-dot memory ... 於 www.ee.nthu.edu.tw -

#59.第七章記憶體和可程式邏輯

記憶體. ✶何謂記憶體. – 儲存格的集合,用來儲存大量二元資訊的一種裝 ... 例子-通常被應用在DRAM積體電路中 ... 當一個組合邏輯電路用一個ROM來設計,它就不需要. 於 www.cyut.edu.tw -

#60.【CMOS積體電路設計概論】(二手書) - 讀冊

TAAZE 單純提供網路二手書託售平台予消費者,並不涉入書本作者與原出版商間之任何糾紛;敬請各界鑒察。 退換貨 ... 於 www.taaze.tw -

#61.矽成積體電路股份有限公司::代理產線 - 大聯大控股

美商矽成積體電路股份有限公司, 為一家專精於記憶體設計與系統整合晶片的IC設計公司, 1990年在台灣成立, 並為全球前十五大靜態隨機存取記憶體供應商(數據來源: ... 於 www.wpgholdings.com -

#62.ICS · ntuee_course_map_105_2 - chengh826

積體電路設計. 開課教授:闕志達; 複選必修(系統類); 推薦同時修習的課程:電子學三; 課程小卦:. ICS入門課程,算是數位ICS很底層的基礎知識(例如加法器、乘法器的 ... 於 chengh826.gitbooks.io -

#63.記憶體電路設計工程師|瑞昱半導體|新竹市 - 104人力銀行

工作項目: 1. FinFET製程記憶體設計開發。 2. 客製化記憶體設計開發。 3. 支援記憶體智財量產性能,良率提升。 應徵條件: 1. 碩士以上; 電機工程、電子工程相關科系 ... 於 www.104.com.tw -

#64.數位積體電路設計 - 政府研究資訊系統GRB

本計畫將從理論分析, 演算法設計, 與積體電路架構設計與實現同時出發探討基於ICA的IBFD的干擾消除演算法與電路架構,以達成更具實用價值的高頻譜效率IBFD系統. 於 www.grb.gov.tw -

#65.國立成功大學- 課程地圖- 半導體記憶體元件與設計實務

開課年度 課程碼 課程名稱 (超連結為課程大綱) 學分數 英語授課 授課教師 0111/1 Q161800 半導體記憶體元件與設計實務 3.0 N 王超鴻,盧達生 0110/1 Q161800 半導體記憶體元件與設計實務 3.0 N 盧達生 0109/1 Q161800 半導體記憶體元件與設計實務 3.0 N 盧達生 於 class-qry.acad.ncku.edu.tw -

#66.產晶積體電路IC設計

產晶積體電路IC設計公司成立於1993年5月,公司位於台北市內湖科技園區,為專業之積體電路IC設計公司。營業範圍主要包括積體電路IC設計、研發與銷售,微控制器MCU,INNO ... 於 www.inno.com.tw -

#67.發展特色 - 國立中央大學電機工程學系

電子組. 研究重點. 人工智慧電子系統設計、超大型積體電路與系統設計、單晶片系統(SoC)電腦 ... 於 www2.ee.ncu.edu.tw -

#68.專訪清大電機系/台積電記憶體電路設計工程師林湘芸(下 ...

「理工的科系很多是用團體面試的方式,聽系上教授的演講,然後會安排一系列的實驗室參觀。」台積電記憶體電路設計工程師林湘芸回顧:「我記得實驗室的 ... 於 article.1221.com.tw -

#69.積體電路設計概論 - 課程大綱查詢- 明新科技大學

介紹積體電路設計基本概念. Introduce basic IC design concept. 課程類別/Course Type: .智慧財產權(Intellectual Property). 系別 ... 於 sss.must.edu.tw -

#70.如何透過堆疊晶片的技術解決快閃記憶體容量不足、減少晶片腳 ...

在電路板設計時,都必須為這些快閃記憶體IC預留焊接空間。 串列式NOR和NAND快閃記憶體因為腳位少,更有利於微小型系統的設計。而華邦電子所 ... 於 www.winbond.com -

#71.半導體產業鏈簡介

由於IC上的電路設計是層狀結構,因此還要經過多次的光罩投入、圖形製作、形成線路與元件等重複程序,才能製作出完整的積體電路。台灣IC製造業者在晶圓龍頭台積電先進 ... 於 ic.tpex.org.tw -

#72.《科技》VLSI國際研討會登場剖析新興記憶體、小晶片系統發展

在經濟部技術處支持下的半導體年度盛事「2021國際超大型積體電路技術研討 ... Unit)與記憶體單元(Memory Unit)分別由不同業者進行設計,並選擇適當 ... 於 events.tku.edu.tw -

#73.CMOS數位積體電路分析與設計(第三版)(0397901) - 金石堂

本書對於CMOS數位IC設計有深入淺出的介紹,並加強對各式記憶體的介紹,對其核心結構及工作原理均有清晰嚴謹的描述。內容包括:MOSFET的製造、MOS電晶體、MOS電晶體 ... 於 www.kingstone.com.tw -

#74.半導體大廠力挺陽明交大前瞻積體電路設計實驗室 - 工商時報

國立陽明交通大學日前(16)日上午攜手技嘉科技與旗下子公司技鋼科技、群聯電子、AMD及SK海力士,於陽明交大舉行捐贈儀式及前瞻積體電路設計實驗室的 ... 於 ctee.com.tw -

#75.[12S035]積體電路設計概論 - 財團法人自強工業科學基金會

IC設計流程與方法 2. 基本元件及佈局原理 3. MOS及MOS電晶體之結構及特性 4. 組合邏輯電路與佈局 5. 時序邏輯電路與佈局 6. 記憶體電路 單元二、類比及混合信號電路及 ... 於 edu.tcfst.org.tw -

#76.數位積體電路分析與設計(第三版) | 誠品線上

數位積體電路分析與設計(第三版) | 誠品線上. Analysis and Design of Digital Integrated Circuits. 作者, David A. Hodges/ Horace G. Jackson/ Resve ... 於 www.eslite.com -

#77.數位積體電路設計 從IC Design的實務面介紹Verilog硬體描述 ...

數位積體電路設計─從IC Design的實務面介紹Verilog硬體描述語言(DVD Inside). +作者:. 夏大維著. +年份:. 2016 年1 版. + ... 於 www.tsanghai.com.tw -

#78.積體電路的「不歸路」 — 全球第四的挑戰 - 天下雜誌

除了記憶晶片的生產之外,台灣的電子工業更需要在積體電路設計能力快速爬升。 工研院電子所所長章青駒分析,儘管國內積體電路設計業者在過去兩年急遽 ... 於 www.cw.com.tw -

#79.剖析5種傳統及3種新型記憶體- 電子技術設計 - EDN Taiwan

本文整理了先前「中國通信積體電路技術與應用研討會暨第二屆晉江國際積體 ... 此外,SRAM、DRAM、FLASH、SONOS和FRAM這五種是基於電荷的記憶體,這類 ... 於 www.edntaiwan.com -

#80.低電壓靜態隨機存取記憶體電路設計及分析

低電壓靜態隨機存取記憶體電路設計及分析. Low Voltage Static Random Access Memory Design and Analysis. 陳銘斌(Ming-Pin Chen) ; 朱元華(Yuan-Hua Ju). 於 www.airitilibrary.com -

#81.記憶體電路設計概論Overview of Memory ... - 課程內容- 臺灣大學

課程概述 ; 課程內容將從記憶體ic的應⽤與發展趨勢開始,進⽽介紹揮發性記憶體sram,dram及非揮發性記憶體rom、flash memory、新興記憶體emerging memory(e.g. mram) 等 ... 於 web.ee.ntu.edu.tw -

#82.什麼是積體電路?— 定義、結構、特性、類型 - 嘉宇科技

積體電路( IC )擁有由半導體、銅和其他材料互連的複雜結構,以形成電阻器、電晶體和其他組件,這些晶片的切割和形成的組合被稱為晶片,構成積體電路的 ... 於 official.kaijui-tech.com -

#83.記憶體電路設計

教學目標. 本課程旨在導引學生建立記憶體晶片電路設計所需要的基礎知識以. 及前瞻記憶體晶片電路設計方法,提供學生記憶體晶片電路設計之. 電路設計基本專業能力;並透過 ... 於 academic.cgu.edu.tw -

#84.77.在DDR3 SDRAM 的記憶體電路設計時,應注意下列哪些 ...

在DDR3 SDRAM 的記憶體電路設計時,應注意下列哪些事項? (A)讓地線自成迴圈以便利接地 (B)插入地線於兩平行線間避免串音干擾 (C)佈線長度不得與訊號波長成整數倍關係 ... 於 yamol.tw -

#85.〔專題演講〕老子說IC設計——全球記憶體大師與李耳的對話 ...

〔專題演講〕老子說IC設計——全球記憶體大師與李耳的對話 ... (現任),南亞科技資深副總,鈺創科技資深副總專長:半導體記憶體電路設計榮譽:行政院88年 ... 於 www2.ck.tp.edu.tw -

#86.系所成員- 專任教師- 國立高雄師範大學電子工程學系

超大型積體電路設計、混合訊號積體電路設計、類比積體電路設計、數位積體電路設計. 聯絡電話. (07)7172930 分機7917. 電子信箱. [email protected]. 於 ee.nknu.edu.tw -

#87.記憶體(RAM)是如何製作的|記憶體晶片 - Crucial TW

晶片的電路元件(電晶體、電阻、和電容器)以層疊方式配置到矽晶圓上。電路經模擬開發與測試,並在電腦系統上完成調校後才正式進行安裝。設計一旦完成後,電路中每一層 ... 於 www.crucial.tw -

#88.積體電路設計 - 學科主題資源

序號 學年度 指導老師 1 109 簡鴻鈞、胡念祖 2 108 林憶霞 3 107 高誌陽 於 subject.lib.mcu.edu.tw -

#89.藉由機器學習突破記憶體發展4 個關鍵瓶頸 - Synopsys

幸運的是,機器學習(ML)在此可成為救星。藉由使用高精度的設計替代模型進行訓練,以預測高sigma電路行為,可以實際減少所需的執行次數。根據已 ... 於 www.synopsys.com -

#90.數位積體電路分析與設計(Analysis and Design of Digital ... - 天瓏

書名:數位積體電路分析與設計(Analysis and Design of Digital Integrated Circuits),ISBN:9861572481,作者:蔣安平、王新安、陳自力、劉欣、黃新,出版社:全華, ... 於 www.tenlong.com.tw -

#91.記憶體 - IisC 物聯網晶片化整合服務中心

以國產晶片元件,搭配開源設計流程,將常用的應用線路製作成模組化的電子零件,提供客戶多樣便利的應用方案。 ... 時脈頻率104 MHz之快閃記憶體(Flash Memory)晶片, 於 iisc.org.tw -

#92.半導體界共同培育高階晶片設計人才力挺陽明交大前瞻積體電路 ...

成立至今已有三十多年歷史的前瞻積體電路設計實驗室(IC Design Lab),每年更是培育超過五百名學生,成為半導體高階IC設計的重鎮。今日支持的企業夥伴, ... 於 n.yam.com -

#93.書籍分類 - 東華書局

CMOS 數位積體電路分析與設計4/e Kang (授權經銷版) ... 本書簡介本書涵蓋層面甚廣,包含半導體製程、元件模型、電路設計、製造測試等相關議題。 於 www.tunghua.com.tw -

#94.ICS組在幹嘛? 2023年電研所積體電路(IC設計組)課程

積體電路與系統組(Integrated Circuits & Systems, ICS),簡稱ICS組,根據ICS組當中細分的專攻領域,在未來研究上或就業上都會有所不同... 於 www.daso.com.tw -

#95.積體電路與系統組 - 電機工程系

組別 姓名 職稱 E‑mail 跨組別領域 教師專長與研究範... 積體電路與系統 黃志良 教授 [email protected] 下載 電信工程 鍾順平 教授 [email protected] 積體電路與系統 下載 積體電路與系統 呂學坤 教授 [email protected] 下載 於 www.ee.ntust.edu.tw -

#96.博碩士論文獎 - TICD 臺灣積體電路設計學會

推廣積體電路設計相關之工程、科學、管理、教育及其他學門之研究應用。並促進國內微電子產業升級,協力發展臺灣積體電路設計工程事業,聯繫國際相關組織並推動學術及 ... 於 ticd.org.tw -

#97.元智大學1111CS378超大型積體電路設計導論

一、課程目標. Course objective, 中, 此課程之目的在讓學生了解CMOS 技術之理論,熟悉數位超大型積體電路系統、各功能模組、基本電路之模式,進而深入研究低耗電、快速 ... 於 portalfun.yzu.edu.tw -

#98.Abstract 作品摘要

研究領域:記憶體內運算電路設計(深度學習人工智慧晶片應用)、記憶. 體積體電路設計、使用記憶體只安全與區塊鏈電路設計、仿生人工智慧晶. 片之憶阻器電路設計、低 ... 於 www.mxeduc.org.tw