window.open close ev的問題,透過圖書和論文來找解法和答案更準確安心。 我們找到下列懶人包和總整理

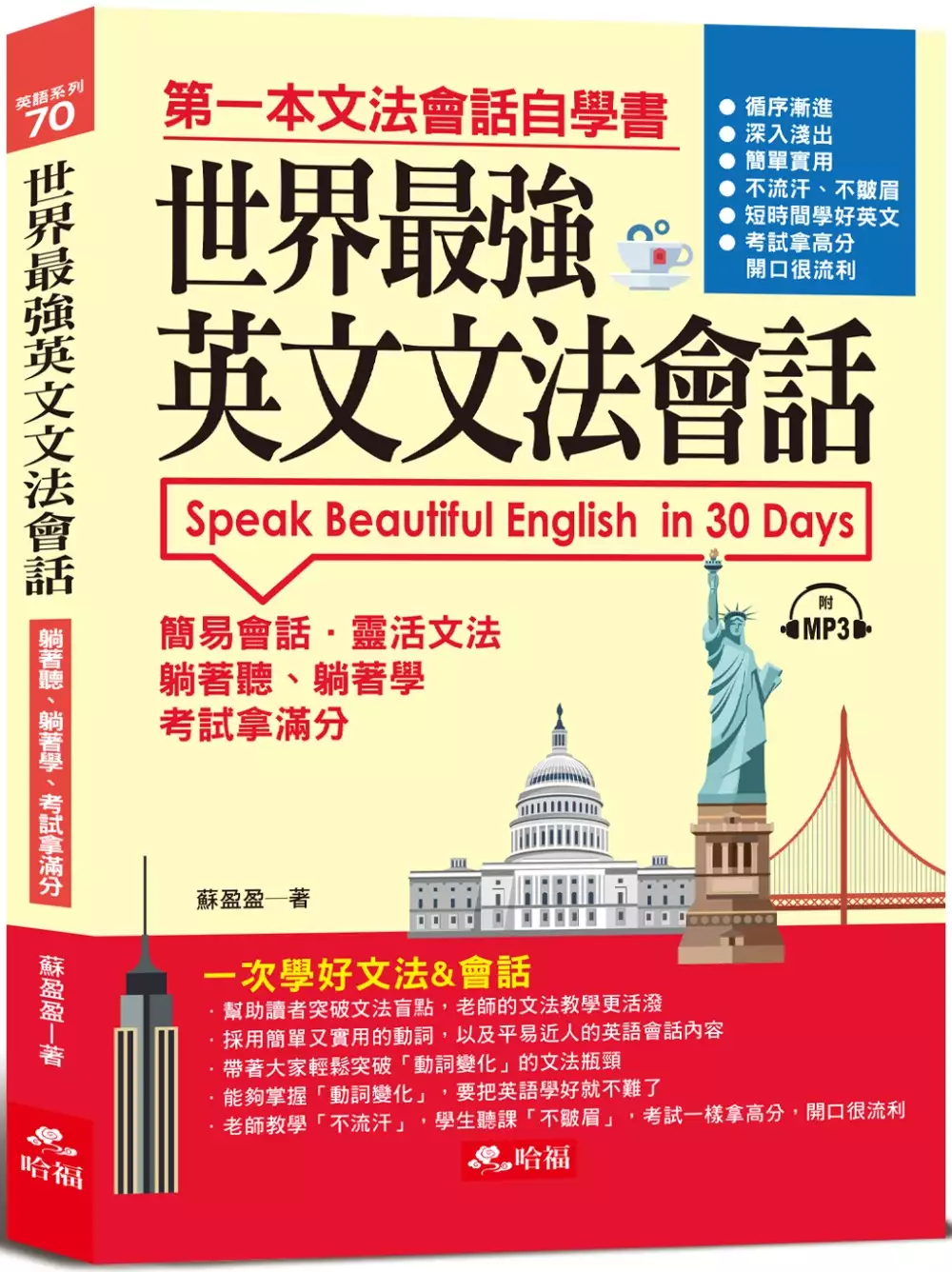

window.open close ev的問題,我們搜遍了碩博士論文和台灣出版的書籍,推薦蘇盈盈寫的 世界最強英文文法會話:一次學好文法&會話(附MP3) 和陳順築的 迢迢路都 可以從中找到所需的評價。

另外網站Your guide to Colorado's electric vehicle cash-for-clunkers ...也說明:Colorado revives “cash for clunkers,” offers $6,000 for an old car you trade for an EV. Piling clunker credits on top of existing state and ...

這兩本書分別來自哈福企業 和田園城市所出版 。

長庚大學 奈米工程及設計碩士學位學程 周煌程、杨杰圣所指導 梁文顏的 低功耗高性能電流式感測放大器設計 (2020),提出window.open close ev關鍵因素是什麼,來自於電流式電路、感測放大器。

而第二篇論文國立臺灣科技大學 化學工程系 黃炳照、楊純誠、蘇威年所指導 Yosef Nikodimos Asgedom的 NASICON和硫化物基固態電解質離子電導率的計算和實驗綜合研究 (2020),提出因為有 鋰離子電池、固態電解質、NASICON型固態電解質、LiGe2(PO4)3、硫化物固態電解質、AIMD模擬、離子傳導率、活化能障、雙重摻雜、水分敏感性的重點而找出了 window.open close ev的解答。

最後網站PlugShare - EV Charging Station Map - Find a place to charge則補充:Find EV charging stations with PlugShare, the most complete map of electric vehicle charging stations in the world!Charging tips reviews and photos from the ...

世界最強英文文法會話:一次學好文法&會話(附MP3)

為了解決window.open close ev 的問題,作者蘇盈盈 這樣論述:

簡易會話.靈活文法 躺著聽、躺著學、考試拿滿分 專為華人設計的第一本文法會話自學書 輕鬆搞定 : TOEIC.TOEFL.IELTS.英檢.學測.會考 也是老師和學生的最佳英語工具書 【最大優點】 ●幫助讀者突破文法盲點,老師的文法教學更活潑 ●採用簡單又實用的動詞,以及平易近人的英語會話內容 ●帶著大家輕鬆突破動詞變化的文法瓶頸 ●能夠掌握動詞變化,要把英語學好就不難了 ●老師教學「不流汗」,學生聽課「不皺眉」,考試一樣拿高分,開口很流利 【給你一把key,進入美麗的英文世界】 你常在英文課裡發呆嗎? 一看到動詞三態就恍神嗎? Daily會

話加上easy文法解析 讓英語腦細胞活蹦亂跳 讓文法與會一起舞動起來 舞出英語的美好人生 【輕鬆學好英文】 ◆簡易會話 靈活文法 1.以循序漸進,深入淺出的編排方式,採用簡單又實用的動詞,及平易近人的英語會話內容,帶大家輕鬆突破的文法瓶頸。 2.搭配專業美語老師所錄製的MP3,邊聽邊學,一定能夠在短短的時間之內學好英文。 ◆不流汗 不皺眉 拿滿分 1. 很多人的英語學習經驗是痛苦的,有了本書「藥到病除」。 除了幫助讀者突破文法盲點,亦能協助英語教師從事更活潑的「文法教學」。 2. 簡而言之,能夠掌握「動詞變化」的人,要把英語學好就不難了。如果

教「文法教學」像在說故事,聊生活,那麼老師也能教學「不流汗」,學生聽課「不皺眉」,考試一樣拿高分,開口一樣很流利。 一本搞定 : TOEIC.TOEFL.IELTS.英檢.學測.會考…,各種考試。 【跟著老美學英語】 本書並聘請專業外籍老師錄製MP3,跟著MP3 聽和學,一句一句跟著大聲說,千萬別閉著嘴巴;用眼睛看著英語學會話,語言是用來溝通的,要開口大聲練習說。要學英語,就是跟著美國人學,他們怎麼說,我們就跟著怎麼說。 要想很輕鬆地學會一口流利的美語,最好的方法是跟著本書由美國專業播音員所錄製的語言MP3唸,而且是大聲地唸,唸久了這些句子自然成了你的語言。

【內容重點】 教您快速學會道地的美語與文法: 1.書中收錄9個章節的文法重點、解說,從現在進行式、現在簡單式、未來式、過去式、過去進行式、現在完成式,全都有詳細解說和互相呼應的對話,善加運用,英語實力進步神速。 2.90個單元的迷你會話,讓您學美語,不僅僅要把它當成中文一樣隨時說,還要學最道地的美語,本書是美語教學專家在美國精心製作,特為中國人學好純正美語和文法者,量身訂做。 本書特色 1. 9大文法重點,詳細解說 2. 簡明扼要,一看就懂 3. 迷你會話,簡單實用,一學就會 4. 循序漸進,深入淺出 5. 不流汗、不皺眉 6. 短時間學好英文

7. 考試拿高分,開口很流利

低功耗高性能電流式感測放大器設計

為了解決window.open close ev 的問題,作者梁文顏 這樣論述:

Table of ContentsRecommendation Letters from Thesis AdvisorsThesis/Dissertation Oral Defense Committee CertificationPreface iiiAbstract ivTable of Contents vList of Figures viiList of Tables xiChapter 1 Introduction 11.1 Memory and Processors 21.2 Sense Amplifiers 31.3 Technology Trends 41.4 Circui

t Trends 51.5 Other Trends 61.6 SRAM Trends 71.7 Associated Challenges 9Chapter 2 A Circuits Survey 102.1 The Two Broad Classes 102.2 Voltage Sensing 122.3 Current Sensing 162.4 Others 20Chapter 3 Development of a Three-Transistor I–V Converter 223.1 Low Drop-Out Voltage Regulator as a I–V Converter

233.2 I–V Converter as a Current Sense Amplifier 253.3 Simplifying the I–V Converter 253.4 Proof of Concept 273.5 Quest for a Better Error Amplifier 293.6 Revisiting the Proof of Concept 31Chapter 4 Implementation of a Current Sense Amplifier 344.1 Sense Amplifier Shut-Down 344.2 Static Power Reduc

tion 364.3 Pulsed Word-Line Operation 374.4 Bit-Line Capacitance—Effect on Delay 394.5 Bias Variation 414.6 Relevant Concerns 43Chapter 5 Conclusion 445.1 Simulation Results 445.2 Considerations for Long Bit-Lines 465.3 Measurements 475.4 Derivative Circuits 495.5 Derivative Use 525.6 Summary 555.7

Final Thoughts 55References 56Appendices 83List of FiguresFigure 1.1 Die micrograph from [Singh et al., 2018] 2Figure 1.2 Layout from [Takemoto et al., 2020] 2Figure 1.3 Package from [Poulton et al., 2019] 4Figure 1.4 Wearable for happiness index from [Yano et al., 2015] 6Figure 1.5 Test chip from [

Song et al., 2017] 7Figure 2.1 Left–right: nMOS common-source, -gate and -drain amplifier configurations 10Figure 2.2 Left–right: pMOS common-drain, -gate and -source amplifier configurations 11Figure 2.3 Bi-stable constructed of two inverters 11Figure 2.4 Regenerative latch transient simulation out

put 11Figure 2.5 nMOS differential pair 12Figure 2.6 nMOS–input pair differential amplifier 13Figure 2.7 Clocked latch with isolation 14Figure 2.8 Current-controlled latch 15Figure 2.9 Left–right: Resistor and nMOS approximates 16Figure 2.10 Left–right: Resistor and pMOS approximates 16Figure 2.11 n

-p-n common-base amplifier 17Figure 2.12 Partial schematic from [Yeo and Rofail, 1995] 17Figure 2.13 Left–right: nMOS and pMOS current mirrors 18Figure 2.14 Current sense amplifier from [Ishibashi et al., 1995] 18Figure 2.15 Current sense amplifier from [Seno et al., 1993] 19Figure 2.16 Current conv

eyor from [Seevinck et al., 1991] 19Figure 2.17 pMOS-neutralised nMOS differential pair 20Figure 2.18 Λ-type negative resistance from [Wu and Lai, 1979] 21Figure 2.19 I D -V D characteristic of the Λ-type negative resistance 21Figure 3.1 Three-transistor I–V converter 22Figure 3.2 Simplified low dro

p-out voltage regulator 23Figure 3.3 Low drop-out voltage regulator configured as a I–V converter 24Figure 3.4 Low drop-out voltage regulator as a current sense amplifier 25Figure 3.5 Reference-free I–V converter 26Figure 3.6 Logic inverters as positive-gain amplifier 26Figure 3.7 Proof of concept d

esign 27Figure 3.8 Proof of concept design transient simulation output 28Figure 3.9 Typical and unintended input(s) of the logic inverter 29Figure 3.10 Normalised absolute gain plot for each inverter input 30Figure 3.11 Connections made for the absolute gain plot 30Figure 3.12 Bias generator for the

absolute gain plot 31Figure 3.13 Error amplifier replacement in the proof of concept design 31Figure 3.14 Three-transistor I–V converter 32Figure 3.15 Corresponding bias generator of Figure 3.14 32Figure 3.16 Simulation circuit for verifying the improved error amplifier 33Figure 3.17 Demonstration

of the three-transistor I–V converter as a current sense amplifier 33Figure 4.1 Actions to achieve desired node characteristics during shut-down 34Figure 4.2 Figure 3.14 modified for shut-down 35Figure 4.3 Corresponding bias generator of Figure 4.2 35Figure 4.4 Shared use of bias generator 36Figure

4.5 Pseudo-differential version of Figure 4.4 37Figure 4.6 Pseudo-differential configuration of Figure 3.14 37Figure 4.7 Pulsed read of a ZERO 38Figure 4.8 Pulsed read of a ONE 38Figure 4.9 Differential development across dynamic bit-lines and csa outputs 39Figure 4.10 Delay behaviour with capacitiv

e bit-line loading 40Figure 4.11 Normalised csa bias current variation with supply voltage 41Figure 4.12 Normalised csa bias current variation with temperature 42Figure 4.13 Mismatch view of Figure 3.14 43Figure 5.1 Test set-up (external trigger connection not drawn) 47Figure 5.2 Oscillogram demonst

rating circuit functionality at VDD = 2.55V 47Figure 5.3 Test set-up photograph 48Figure 5.4 Left–right: Three-transistor I–V converter and its complement 49Figure 5.5 Transfer characteristics of the circuits in Figure 5.4 49Figure 5.6 Four-transistor I–V converter 50Figure 5.7 Corresponding bias ge

nerator of Figure 5.6 50Figure 5.8 Impact of sizing on AC performance 51Figure 5.9 Left–right: V SS -, V DD -referenced and floating optical receiver front ends 52Figure 5.10 Transfer characteristic of floating I–V converter 53Figure 5.11 High output resistance eases filter realisation 53Figure 5.12

Three-transistor I–V converter operating as an open-drain receiver 54Figure A.1 inv symbol 84Figure A.2 Alternate inv symbol 84Figure A.3 inv transistor-level schematic 84Figure A.4 inv4 symbol 85Figure A.5 inv4 transistor-level schematic 85Figure A.6 inv16 symbol 86Figure A.7 inv16 transistor-leve

l schematic 86Figure A.8 nand2 symbol 87Figure A.9 nand2 transistor-level schematic 87Figure A.10 nand2b symbol 88Figure A.11 nand2b gate-level schematic 88Figure A.12 nor2 symbol 89Figure A.13 nor2 transistor-level schematic 89Figure A.14 nor2b symbol 90Figure A.15 nor2b gate-level schematic 90Figu

re A.16 or2 symbol 91Figure A.17 or2 gate-level schematic 91Figure A.18 tinv symbol 92Figure A.19 tinv transistor-level schematic 92Figure A.20 dlat symbol 93Figure A.21 dlat gate-level schematic 93Figure A.22 dlatr symbol 94Figure A.23 dlatr gate-level schematic 94Figure A.24 dlats symbol 95Figure

A.25 dlats gate-level schematic 95Figure A.26 tie0 symbol 96Figure A.27 tie0 transistor-level schematic 96Figure A.28 tie1 symbol 97Figure A.29 tie1 transistor-level schematic 97Figure B.1 bit0 symbol 99Figure B.2 bit0 transistor-level schematic 99Figure B.3 bit1 symbol 100Figure B.4 bit1 transistor

-level schematic 100Figure B.5 blrc symbol 101Figure B.6 blrc cell-level schematic 101Figure B.7 pre symbol 102Figure B.8 pre transistor-level schematic 102Figure B.9 rblrc symbol 103Figure B.10 rblrc cell-level schematic 103Figure B.11 wr symbol 104Figure B.12 wr transistor-level schematic 105Figur

e B.13 anand2 symbol 106Figure B.14 Alternate anand2 symbol 106Figure B.15 anand2 transistor-level schematic 107Figure B.16 ckgen symbol 108Figure B.17 ckgen gate-level schematic 108Figure B.18 peri symbol 109Figure B.19 peri cell-level schematic 110Figure B.20 csa symbol 111Figure B.21 csa transist

or-level schematic 111Figure B.22 kobl symbol 112Figure B.23 Alternate kobl symbol 112Figure B.24 kobl transistor-level schematic 113Figure B.25 kobs symbol 114Figure B.26 kobs transistor-level schematic 114Figure C.1 sram1 symbol 116Figure C.2 sram1 block-level schematic 117Figure C.3 sram2 symbol

118Figure C.4 sram2 block-level schematic 119Figure C.5 sram3 symbol 120Figure C.6 sram3 block-level schematic 121Figure D.1 ainvl symbol 123Figure D.2 ainvl transistor-level schematic 123Figure D.3 ainvs symbol 124Figure D.4 Alternate ainvs symbol 124Figure D.5 ainvs transistor-level schematic 124F

igure D.6 cut symbol 125Figure D.7 cut cell-level schematic 126Figure D.8 inAmp symbol 127Figure D.9 inAmp cell-level schematic 127Figure D.10 CD4007 symbol 128Figure D.11 CD4007 transistor-level schematic 128Figure D.12 LF356 symbol 129Figure D.13 LF356 cell-level schematic 129Figure D.14 TL431 sym

bol 130Figure D.15 TL431 cell-level schematic 130Figure D.16 tialp symbol 131Figure D.17 tialp transistor-level schematic 131Figure D.18 tiasd symbol 132Figure D.19 tiasd transistor-level schematic 132Figure D.20 tiasn symbol 133Figure D.21 tiasn transistor-level schematic 133Figure D.22 tiasp symbo

l 134Figure D.23 tiasp transistor-level schematic 134Figure E.1 nfet and equivalent nMOS symbol 135Figure E.2 pfet and equivalent pMOS symbol 136Figure E.3 Circuit for estimating per-bit junction capacitance 137Figure E.4 Simulation output for estimating per-bit junction capacitance 138Figure E.5 Ci

rcuit for estimating per-bit bit-line leakage current 138Figure E.6 ID-VD characteristics 139Figure E.7 ID-VG characteristics 140Figure E.8 anand2 transistor-level schematic 141Figure E.9 Test board functional blocks 144Figure E.10 Test board block-level schematic 145Figure E.11 Signal source connec

ted to abbreviated input network 148Figure E.12 General form of a typical instrumentation amplifier 150Figure E.13 Inverting integrator section of test board 154List of TablesTable 1.1 Semiconductor memory hierarchy 1Table 5.1 Column height h = 512b 44Table 5.2 Column height h = 1Kb 44Table 5.3 Colu

mn height h = 2Kb 44Table 5.4 Summarised measurement results 48Table A.1 List of standard cells 83Table A.2 inv truth table 84Table A.3 inv4 truth table 85Table A.4 inv16 truth table 86Table A.5 nand2 truth table 87Table A.6 nand2b truth table 88Table A.7 nor2 truth table 89Table A.8 nor2b truth tab

le 90Table A.9 or2 truth table 91Table A.10 tinv truth table 92Table A.11 dlat truth table 93Table A.12 dlatr truth table 94Table A.13 dlats truth table 95Table A.14 tie0 truth table 96Table A.15 tie1 truth table 97Table B.1 List of custom cells 98Table B.2 pre truth table 102Table B.3 wr truth tabl

e 104Table C.1 SRAM cells and read path configurations 115Table D.1 List of other cells 122Table E.1 Transistor performance 140Table E.2 Primary bill of materials 146Table E.3 Additional hardware 147Table E.4 List of instruments 155Table F.1 List of abbreviations 158Table F.2 List of symbols 159Tabl

e F.3 List of AC quantities 160Table F.4 List of DC quantities 161Table F.5 List of partial-swing signals 162Table F.6 List of rail–rail signals 162Table F.7 List of instance names 163

迢迢路

為了解決window.open close ev 的問題,作者陳順築 這樣論述:

二十年來的攝影歷程,除了訓練陳順築一對銳利的眼睛,也令他掌握了一種如何展現自己情感和世界觀的方式。--節錄自 艾阮 文章「陳順築,一個拾取記憶斷片的旅人」 它們全是抽象化的異鄉,與圖案化的家鄉。在無人的、抽象的、美術化的風景照片裡,陳順築展現出一種寂靜、孤獨、唯美、秩序、理性的氣質。--節錄自 郭力昕 文章「從家族影像到冷凝的《迢迢路》」 儘管是靜態影像,我們在感知上仍可彌平那些不連續時序之間的大量空缺,在想像「旅程」之餘,感覺到平滑的時間感和一個瞬息萬變、似近又遠的世界。--節錄自 鄭慧華 文章「曖昧日常中的生活詩學─陳順築攝影系列《迢迢路》」 我們大約可以把陳順築這一組

作品定位於一種以美學導向為主的風景攝影……,他的風景攝影不只在於探討攝影的視覺特質,也加入了另一個面向,即「自我」這個層面。--節錄自 林志明 文章「讀陳順築作品《迢迢路》」 Two decades of photograph career not only trains Chen Shun-Chu to have sharp eye, but also leads him to develop an approach to express his own affection and his viewpoint toward this world. Extract from the a

rticle “Chen Shun-Chu, A Traveler Picks up Fragments of Memories”--Ai Juan They are all abstractive foreign lands and patterned hometowns. In those unpeopled, abstractive, and artistically stylized landscape photographs, Chen Shun-Chu presents a quiet, lonely, aesthetic, ordered, and rational qual

ity. Extract from the article“From Family Images to the Chill-toned On the Road”-- Kuo Li-Hsin Although those are merely motionless images, in our perception we still could make up the huge vacuum among those non-successive fragments of time and space and feel the smooth time sequence and a cons

tantly-changing world that is seemingly so close and yet sometimes very remote, on our imaginary “journey”. Extract from the article “The Poetics of Life in the Ambiguous Routine About the New Photography Series On the Road by Chen Shun-Chu” -- Amy Cheng We could roughly position Chen Shun-Chu’

s new collection of works as aesthetics-oriented landscape photography..., his landscape photographs not only discuss the visual characters of photography, but also include a “self” perspective. Extract from the article“Reading On the Road by Chen Shun-Chu”--Lin Chi-Ming 作者簡介 陳順築 1963 台灣澎湖出生,目前創

作與生活在台北 1986 中國文化大學,美術系西畫組畢業 1995 獲「台北美術獎」 台北市立美術館 2009 獲「李仲生視覺藝術獎」 李仲生現代繪畫文教基金會 2005 - 德霖技術學院,營建科技系空間設計組 專任副教授 2005 - 2008 國立台中教育大學,美術系所 兼任副教授 2006 - 2008 東海大學,美術系所 兼任副教授 2008 - 國立台灣藝術大學,美術研究所 兼任副教授 1963 Born at Penghu , Taiwan. Currently live and work in Taipei. 1986 Graduated from Chine

se Culture University with a B.F.A. degree in Painting 1995 Received Taipei Arts Award, Prizewinner, Taipei Fine Arts Museum 2009 Received Li Chung-Shen Foundation Visual Art Awards, Li Chung-Shen Modern Painting Foundation 2005- DeLin Institute of Technology, Department of Construction Science

and Technology, Associate Professor 2005 - 2008 National Taichung University, Department of Fine Arts, Adjunct Associate Professor 2006 - 2008 Tunghai University, Department of Fine Arts, Adjunct Associate Professor 2008- National Taiwan University of Arts, Department of Fine Arts, Adjunct Asso

ciate Professor

NASICON和硫化物基固態電解質離子電導率的計算和實驗綜合研究

為了解決window.open close ev 的問題,作者Yosef Nikodimos Asgedom 這樣論述:

LiGe2(PO4)3(LGP)是一種NASICON型氧化物固態電解質,是下一代二次儲能固態鋰電池最有希望的固態電解質候選人之一。 在所有固態鋰電池中使用均具有許多優勢,例如出色的電化學和熱穩定性。 然而,其具有較大的晶界阻抗致使低的離子電導率是阻礙其在商業上實際應用的主要挑戰之一。 因此,由於離子電導率是主要的限制之一,因此是實際應用時須率先克服的問題。本論文中,第一種方法中通過實驗和理論計算添加不同數量的Al和Sc對LGP的鋰離子電導率的影響。以Li1 + x + yAlxScyGe2-x-y(PO4)3形式的Sc3 +和/或Al3 +離子代替LGP結構中25%的Ge4 +離子,其中x

+ y = 0.5,此可在M2空位中得到更多的鋰離子位(36f位)並提升電解質的離子電導率。在兩種計算結果中,Li1.5Al0.33Sc0.17Ge1.5(PO4)3所得到的鋰離子電導率最高,實驗值為5.826 mS cm-1,理論值為6.836 mS cm-1。此外,使用Nudged Elastic Band進一步闡述了活化能和其最低值,該組成提供了最低之活化能0.279 eV。 Li1 + x + yAlxScyGe2-x-y(PO4)3材料是使用熔融淬火方法製造的,並分別通過電化學阻抗譜、X光繞射和循環伏安法表徵了鋰離子電導率、晶體結構和電化學勢窗。其離子電導率,活化能和電化學勢窗的實驗

測量與計算結果具有一致性。最後,組裝固態電池以測試循環性能。在第二種方法中,使用Mg元素摻雜於LAGP形成新型化合物Li1 + x + 2yAlxMgyGe2-x-y(PO4)3(LAMGP)。根據計算結果,合成了最佳的離子導電組合物(Li1.6Al0.4Mg0.1Ge1.5(PO4)3並應用於實驗工作。 相對於原始材料LAGP(2.989 mS cm-1),它提供了超高的整體離子電導率(7.435 mS cm-1)與更好的緻密性,具有較低的晶界阻抗。 與使用LAGP做為電解質組裝的固態電池相比, LAMGP的固態電池具有出色的循環性能。 另外,分析LAMGP經過電池循環後的界面證實了於負極/

電解質介面形成了一層新型的SEI且其會被鋰金屬還原,這有助於LAMGP體系的固態電池的長圈電化學循環性。此外,同樣為熱門固態電解質材料的的硫化物基固態電解質同樣是下一世代極具潛力的固態電解質之一。與氧化物固態電解質相比,具有更高的導離度,非常接近液態電解質,然而,仍有許多問題待解決。因此,於本論文中我們藉由第一性原理計算進行了一系列篩選摻雜元素,以研究幾種選定的摻雜劑對Li3PS4固態電解質的離子電導率和水分穩定性的影響。由結果表明,使用電負度較接近S2-的等價陽離子取代P5 +,對離子電導率性能有極好的影響,其中W5 +和Sb5 +實現了很高的離子電導率改善。同樣地,具有補償鋰離子濃度變化的

異價陽離子取代,特別是具有較低氧化態和較高電負性的那些,例如Cu 2+,也對該結構中的鋰離子電導率具有正面的影響。對於陽離子摻雜劑,我們發現Li3PS4的離子電導率提高是摻雜劑的電負度、氧化數以及材料晶格參數變化的協同效應。另外,使用陽離子的氧化物作為摻雜劑也能夠改善材料的離子電導率,但是具有比其對應的陽離子摻雜劑低的鋰離子電導率。另一方面,金屬氧化物摻雜劑在Li 3 PS 4電解質的水分穩定性方面也顯示出少量改善。我們還研究了鹵化物和金屬鹵化物摻雜劑對Li3PS4電解質的鋰離子電導率和水分穩定性的影響。從結果中發現金屬鹵化物在改善Li 3 PS 4的離子電導率方面具有比任何其他摻雜劑大得多的

作用。基於這些結果,我們得出結論,金屬鹵化物是提高離子電導率的理想選擇,而陽離子的金屬氧化物對於穩定Li3PS4硫化物固態電解質的水分敏感性則更為有效。

想知道window.open close ev更多一定要看下面主題

window.open close ev的網路口碑排行榜

-

#1.FIAT® USA Official Site | Crossovers and Cars

... My Garage(Open in a new window) · My Vehicle Orders · My Profile; Logout ... FIND A DEALER; SHOP ONLINE(Open in a new window); BUILD & PRICE. close. 於 www.fiatusa.com -

#2.Window: close() method - Web APIs - MDN Web Docs - Mozilla

Closing a window opened with window.open(). This example shows a method which opens a window and a second one which closes the window; ... 於 developer.mozilla.org -

#3.Your guide to Colorado's electric vehicle cash-for-clunkers ...

Colorado revives “cash for clunkers,” offers $6,000 for an old car you trade for an EV. Piling clunker credits on top of existing state and ... 於 coloradosun.com -

#4.PlugShare - EV Charging Station Map - Find a place to charge

Find EV charging stations with PlugShare, the most complete map of electric vehicle charging stations in the world!Charging tips reviews and photos from the ... 於 www.plugshare.com -

#5.How to Use the Ford Global-Open Windows Feature - Akins Ford

Closing Windows – Change your mind about opening all those windows? No problem! Closing them back up is just as easy. Just press and hold the ... 於 www.akinsford.com -

#6.PMHC powers ahead with EV charging stations

Port Macquarie-Hastings Council (PMHC) has installed two dedicated electric vehicle (EV) charging stations at its Lord St carpark to assist ... 於 www.pmhc.nsw.gov.au -

#7.Hyundai TUCSON | Hyundai Motor UK

The Hyundai TUCSON compact SUV features advanced, progressive design, state-of the-art technology and an electrified powertrain line-up. 於 www.hyundai.com -

#8.Remote window closing/opening

Operation. Press and hold the door lock button on the smart key to close the windows. The windows will move up as long as the button is pressed. 於 www.kia.com -

#9.Can anyone challenge China's EV battery dominance?

People close to the negotiations said the companies had also weighed risks posed by US-China tensions in debating where to procure batteries ... 於 www.ft.com -

#10.Duke Energy unveils EV charging subscription service ...

Electric vehicles at an EV charging station. ... Duke, with GM, Ford and BMW, is using the Open Vehicle Grid Integration Platform, or OVGIP, ... 於 www.utilitydive.com -

#11.Investigating Groundwater - 第 438 頁 - Google 圖書結果

The energy of radiation is measured in electron volts (ev). ... That is, they receive energy from a window open to the side of the borehole. 於 books.google.com.tw -

#12.Tesla to Remove Window Auto-Close Features Due to New ...

An updated Federal regulation from the NHTSA no longer allows for auto-close windows via the car or an app, among other features. 於 www.notateslaapp.com -

#13.Washington State Department of Transportation

Travel Open submenu; Construction & planning Open submenu; Business with WSDOT Open submenu; Engineering & standards Open submenu; About Open submenu. Close ... 於 wsdot.wa.gov -

#14.Diablo 4 crash codes. 5. Left click on the shortcut tab. Sele

The Diablo IV studio issued a heads-up prior to this weekend's open beta that ... I did a clean windows 11 install, with the latest updates and drivers and ... 於 camaraibema.pr.gov.br -

#15.Any way to disable auto window? - My Nissan Leaf Forum

A light push/pull on the button will adjust window to desired height, if you push/pull harder it will go into auto mode (full open or close). 於 mynissanleaf.com -

#16.Windows 11 this pc folders missing. Note: Files deleted from ...

Please help me to turn on Favorites and Recent in File Explorer in my laptop running Windows 11. 5 You will now see a command prompt open and close to kill ... 於 kosazeneiskola.hu -

#17.Using Vehicle Monitor and Alert - Connected Service Manual

8 Trunk/Liftgate Status: Displays the trunk/liftgate open/close status. ... 11 Front Defroster: Displays the front window defroster status. 於 www.mazdausa.com -

#18.Europe New Car Registrations Rise Further Amid Massive EV ...

(RTTNews) - The European car market continued to log double-digit sales growth in July amid the rising demand for battery electric vehicles, ... 於 markets.businessinsider.com -

#19.Project STAR: The Universe in Your Hands. Teacher's guide ...

... place this near a window and turn off the classroom fluorescent lights . ... of an incandescent lightbulb extends from about 2.9 e.v. to around 1.7 e.v. ... 於 books.google.com.tw -

#20.Job vacancies, quits plunge in July in stark sign of cooling ...

Businesses posted far fewer open jobs in July and the number of ... a Panasonic EV battery plant Thursday, May 18, 2023, near DeSoto, Kan. 於 www.local10.com -

#21.SDK Platform Tools release notes | Android Studio

Download SDK Platform-Tools for Windows ... Disables an error message that occurred when fastboot attempted to open the touch bar or keyboard on macOS. 於 developer.android.com -

#22.OWNER'S MANUAL - Tata Nexon EV

OPENING AND CLOSING. Keys. 45. Doors. 49. Windows. 50. Bonnet Opening. 52. Tail Gate Opening. 53. Opening Battery Charge Flap. 於 nexonev.tatamotors.com -

#23.Window open() Method - W3Schools

The open() method opens a new browser window, or a new tab, depending on your browser settings and the parameter values. See Also: The close() method. Syntax. 於 www.w3schools.com -

#24.Up Close with the 2025 Volvo EX30 - TractionLife.com

Volvo is set to launch its latest EV in the EX30, its “smallest ever SUV” and one that sticks to the brand's focus on safety and ... 於 tractionlife.com -

#25.EuroVision Windows Operation Instructions - StyroMAX

EuroVision Window Operation Instructions. ○ Open Window Instructions. Step1: Push button on the handle and rotate handle to ... Close Window Instructions. 於 styromax.com.au -

#26.The Encyclopaedia Britannica: Or, Dictionary of Arts, ...

If the eye is close to the lens it will see the object which it views as distinctly as ... and sometimes the shape of a Gothic window has been given to them ... 於 books.google.com.tw -

#27.Global window open / close from key fob

This was discussed in an earlier post - how to have windows open and close from the key fob on US vehicles that aren't set that way from ... 於 www.myfocuselectric.com -

#28.Rodeo EV Charging Capacity Doubles With New Ports

Now, the world's largest and most open EV charging network in North America, ... Next⇒ Water Service Shut Off Along Portion of Oak Street ... 於 www.steamboatsprings.net -

#29.Switch Delhi - Find a charging station near you

The Open Database is a unified and dynamic database offering historical and real time information for EV charging and swapping stations in the NCT of Delhi. 於 ev.delhi.gov.in -

#30.Window opening / closing with key - Speak EV

If you press and hold the "open" symbol, the door will open and if you wait a short while (still holding down the "open" symbol) all the windows ... 於 www.speakev.com -

#31.Hold the open button to open the windows | Kia EV6 Forum

Unfortunately, you can't close them the same way. Click to expand... You can by holding the lock button. Reply. 於 www.kiaevforums.com -

#32.Explained: That Weird Throbbing When You Open One Car ...

Why is the wind buffeting so bad when one window is rolled down in your car? 於 www.caranddriver.com -

#33.FACT SHEET: Biden-Harris Administration Announces New ...

Effective immediately, all EV chargers funded through the Bipartisan ... Tesla, for the first time, will open a portion of its U.S. ... 於 www.whitehouse.gov -

#34.Should You Open Your Windows When the AC is on?

If the open window is near a thermostat, that room will be impossible to cool, since hot air is constantly pouring in. While the AC is working to cool down ... 於 reimerhvac.com -

#35.Teslas Will Soon Automatically Close Parked Car Windows In ...

Now, a feature for Tesla vehicles will automatically close any open windows if it detects that it's raining and save your interior from ... 於 www.carscoops.com -

#36.Duke Energy to pilot EV charging subscription service in North ...

Duke Energy's 12-month EV Complete Home Charging Plan pilot will allow ... Ford Motor Company and BMW of North America as a part of the Open ... 於 news.duke-energy.com -

#37.Find every public charging station for electric cars | ChargeHub

The ChargeHub charging stations map allows you to find all the available electric vehicle (EV) public charging stations near you when you need to charge ... 於 chargehub.com -

#38.2024 Chevrolet Blazer EV vs Other Vehicles - Details - Autoblog

Compare Details of the 2024 Chevrolet Blazer EV 2LT All-Wheel Drive ... Sunroof, 1st And 2nd Row Exterior Express Open/close Sliding And Tilting Glass. 於 www.autoblog.com -

#39.Window Open. | Jaguar I-Pace Forum

My I-Pace App is happy to inform me that I have left a window open. Is there any way to close that offending window from the app? 於 www.ipaceforums.co.uk -

#40.QWindow Class | Qt GUI 6.5.2

The QWindow class represents a window in the underlying windowing system. ... Override this to handle close events (ev). 於 doc.qt.io -

#41.Xiaomi's president says its EV manufacturing progress is ...

Xiaomi Group's president Lu Weibing said on Tuesday that the company's electric vehicles have finished summer testing and made more progress ... 於 technode.com -

#42.EY US - Home | Building a better working world

Close Modal Dialog. Beginning of dialog window. Escape will cancel and close the window. Text. Color. White, Black, Red, Green, Blue, Yellow, Magenta, Cyan. 於 www.ey.com -

#43.[JAVASCRIPT]偵測你的windows.open是否關閉了closed

[JAVASCRIPT]偵測你的windows.open是否關閉了closed ... ://stackoverflow.com/questions/31513828/how-to-detect-popup-window-close-event/38165968. 於 dotblogs.com.tw -

#44.ChargePoint: EVSE | Electric Vehicle (EV) Charging Stations

ChargePoint is the world's largest network of electric vehicle (EV) charging stations in North America and Europe. Join the EV revolution for a greener ... 於 www.chargepoint.com -

#45.Quickly Close Open Windows Using Shortcut Keys - Lifewire

How to Close Windows With Alt + Spacebar + C. One option for closing windows with keyboard shortcuts is as follows: Open the window that you ... 於 www.lifewire.com -

#46.Worse for range: AC or windows open? : r/electricvehicles

Speeds may not be the same for an EV though, but the general principle applies. The higher the speed the better for AC. 於 www.reddit.com -

#47.Her Last Words: An addictive psychological thriller that ...

E.V. Kelly. going though, on up the road, until she is standing outside his house. The name is not on the gate post but she knows that this one is his. 於 books.google.com.tw -

#48.Irving Interchange Closures Aug. 28-Sept. 1

Southbound Loop 12 will be closed from SH 183 to Grauwyler Road, from Wednesday, Aug. ... Get Road Construction Alerts Opens in new window ... 於 www.cityofirving.org -

#49.i-Smart 2.0 Technology | 70+ Connected Car Features

REMOTE ALL WINDOWS OPEN/CLOSE. Put the window up or down with using the i-Smart App. ×. MG Motor India website uses cookies. 於 www.mgmotor.co.in -

#50.Electric Vehicle Rebate Program

EV rebates are subject to the availability of funds for each cycle. ... The next application period will open on November 1, 2023 and close January 31, ... 於 epa.illinois.gov -

#51.Global Open/close Windows | 2023 Ford Explorer Videos

Your vehicle may have a feature that lets you open or close your windows with your key fob to help cool the inside of your car before you get in. 於 www.ford.ca -

#52.Mercedes-Benz Will Open Its First EV Charging Station Later ...

Mercedes-Benz announced big plans to build a worldwide charging network for electric vehicles earlier this year, and things are finally ... 於 www.howtogeek.com -

#53.Seventy Years of Double Beta Decay: From Nuclear Physics to ...

For (mv) < 1 eV we find the following lower bounds: T^Ge) > 1.85 X 1 25 yr, ... we expect the matrix element and therefore the half-life to be close ... 於 books.google.com.tw -

#54.Windows slightly opening when opening/closing door...

Once the door is closed, it's a fixed load to slide the window up. ... Could tint and leave doors open until set but seems ridiculous to not ... 於 www.mybmwi3.com -

#55.Large-bandgap organic semiconductors with trap-free charge ...

Organic semiconductors have been found to have an energy window of only 2.5 eV (corresponding to an electron affinity higher than 3.5 eV and ... 於 www.nature.com -

#56.α7C II compact full-frame camera - Sony Corporation

Exposure correction value, +0.0 EV. Exposure program, Manual exposure. Metering mode, Multi segment. ISO, 100. White balance settings, Manual ... 於 www.sony.net -

#57.A DICTIONARY OF THE ENGLISH LANGUAGE

Forc'd from windyuns , lead itself can fly , Ere I let fall the windows of ... When you leave the windows open for air , leave Soutb . from his reason . 於 books.google.com.tw -

#58.Electric Vehicle Charging Station Locations

Find electric vehicle charging stations in the United States and Canada. For Canadian stations in French, see Natural Resources Canada. Close ... 於 afdc.energy.gov -

#59.Window open detection - Beginners - openHAB Community

Hi there, just wanted to ask you for a window detection algorithm based ... method will struggle to detect when the window is closed again. 於 community.openhab.org -

#60.Cool Down your Ford, Before You Get In

Open /close all of your vehicle's windows right from the key fob. When you are in range of your vehicle, press and hold the unlock button for ... 於 www.islandford.ca -

#61.Electric Vehicle (EV) and EV Charging Station Data - NYSERDA

Link opens in new window - close new window to return to this page. . NYSERDA Charging Station Demonstration Data. In 2012 and 2013, NYSERDA awarded $8 million ... 於 www.nyserda.ny.gov -

#62.Saving fuel: Windows down or air con on, which is better?

Above this speed, the drag effect of the windows being open, begins to make it more fuel efficient to shut them in favour of switching on ... 於 leasing.com -

#63.In an electric car, does it consume less electricity to open the ...

A EV is typically a car designed with a low CD. Open windows are drag inducing, and represent a greater effect on the EV than your typical car. 於 www.quora.com -

#64.Opening windows from the renderer | Electron

Windows can be created from the renderer in two ways: ... If set to true , the newly created window will not close when the opener window closes. 於 electronjs.org -

#65.DALL·E 2 - OpenAI

Close. Search Submit. Skip to main content. Site Navigation ... Mobile Navigation. Close. Site Navigation ... This opens in a new window. 於 openai.com -

#66.Action Required. Open and close driver side window.

2017 Bolt EV Silver Ice Metallic, Premium, Infotainment pkg, ... Open and Close the driver's side window is required to restore the auto up ... 於 www.gm-volt.com -

#67.Public invited to meeting about two City sidewalk projects

City of Clarksville making streets safer near new Arena ... Women of Clarksville Expo returns in August, vendor applications open now. 於 www.cityofclarksville.com -

#68.The Window Is Closing for EV Startups - Road & Track

Even the most established and best-positioned EV startups -- Lucid and Rivian ... That open window for start-ups is suddenly slamming shut. 於 www.roadandtrack.com -

#69.Autoclose opened windows feature on car close is missing?

In case windows are not fully closed and you're leaving the car, windows remains open after closing car (by pressing button on door handle ... 於 www.ioniqforum.com -

#70.Electric Vehicles - SP Energy Networks

What an EV is; Some important impacts of EVs; What kind of EV chargers are available; How you can connect an EV charger to the network; Answers to EV FAQs ... 於 www.spenergynetworks.co.uk -

#71.Kia EV6 How to remote open/close the front windows - YouTube

How to remote open / close the front windows using the smart key.When i say press the open button i really ... EV Odessey. 3.93K. Subscribe. 於 www.youtube.com -

#72.BP

Our purpose is reimagining energy for people and our planet. We want to help the world reach net zero and improve people's lives. We want to be an energy ... 於 www.bp.com -

#73.A Guide for Safe Electrical Testing for Electric Vehicle (EV ...

Zero-voltage measurement. This measurement is conducted to prevent electric shock and to make sure that the vehicle is shut down. Measure the voltage on ... 於 www.hioki.com -

#74.eMobility charging- Siemens global website

Let's explore and debate the latest developments in EV technology and the challenges and ... We took a close look at the city of Munich, Germany, ... 於 www.siemens.com -

#75.How to close an undesired opened window/tab #1096 - GitHub

Println("New page open at: ", ev.URL) go func() { if err := chromedp.Run(ctx, chromedp.Sleep(2 * time.Second), page.Close(), ); err != nil ... 於 github.com -

#76.First-Ever Silverado EV Electric Truck - Chevrolet Canada

Actual production model may vary. 2024 Silverado EV RST anticipated availability early 2024. ... See Silverado EV up close ... SAY HELLO TO THE OPEN ROAD. 於 www.chevrolet.ca -

#77.Should I use A/C or open my windows? - Fuel Card Services

Having the A/C on and windows open isn't particularly economical. ... the air-con will be more effective if you keep the windows closed. 於 www.fuelcardservices.com -

#78.Global Window Open/Close function via ForScan?

Hey y'all! I've been trying to get global window open/close functioning with FORScan today, but I can't seem to get it to work using the old ... 於 www.f150lightningforum.com -

#79.Can Electric Car Windows Open on Their Own? All You Need ...

Yes, electric car windows can open on their own. ... Some cars have a system to either open the window or stop closing it if any obstruction ... 於 findingev.com -

#80.Window open closing with key Fob MG4 Trophy

Press and hold open to lower windows; press and hold close to raise windows. That's the usual way with most cars. Reply. 於 www.mgevs.com -

#81.Javascript Window Open() & Window Close() Method

open () and window.close() method in Javascript. If you click on the Open GeeksforGeeks button then the geeksforgeeks.org page opens in a new ... 於 www.geeksforgeeks.org -

#82.How do I get around window.opener cross-domain security

But don't close the child window by itself. Let the opener window obtain the result from the child window and then close it. 於 stackoverflow.com -

#83.Nanomaterials-Based Charge Trapping Memory Devices

∆E = 2.51 eV ∆EC = 2.44 eV Blocking oxide Al 2 O3 0.07 eV Si Eg Ef = 1.12 eV ... charges leak out after 104 cycles where a 4 V memory window is measured. 於 books.google.com.tw -

#84.TE Connectivity: Connectors & Sensors for a Connected ...

Beginning of dialog window. Escape will cancel and close the window. Text. Color. White, Black, Red, Green, Blue, Yellow, Magenta, Cyan. Transparency. 於 www.te.com -

#85.Windows - Tesla

Learn how to open, close, lock and calibrate your vehicle windows. ... If a window is left open unintentionally, Model Y can send a notification to the ... 於 www.tesla.com -

#86.Synthesis of Ni3B/Ni via Vacuum‐Induced for Ultrahigh Stable ...

The peak at 188 eV is attributed to Ni3B in the B 1s spectrum ... by reducing Ni 2+ with NaBH4 in an open atmosphere with air (step 1). 於 onlinelibrary.wiley.com -

#87.U.S. Senator blocks bid to close EV tax window - Reuters

Senator Debbie Stabenow thwarted a bid on Thursday by fellow Democrat Joe Manchin to pass a measure that would block some electric vehicles ... 於 www.reuters.com -

#88.ESP-F - spedtrans.hu

My previous discord account was closed due to hacking. ... EMS-ESP is an open-source firmware for the Espressif ESP8266 and ESP32 microcontroller that ... 於 spedtrans.hu -

#89.Infinity Roof Removal | HUMMER EV Quick Start Guide - GMC

Close the hood. Removing the Front I-Bar: †. First, remove the front roof panels. Keep your windows open while removing ... 於 www.gmc.com -

#90.Small EV maker becomes more valuable than Ford, GM ...

His stake in VinFast was worth US$86.7 billion as of Monday's close in New York. Combined with the remainder of his wealth, which would have put ... 於 www.stuff.co.nz